電磁気学入門(11)フライバッククランプ回路と関連の損失:DC-DCコンバーター活用講座(54)(1/2 ページ)

電磁気学入門講座。今回は、フライバッククランプ回路および関連の損失について解説します。

フライバッククランプ回路および関連の損失

連載第5回の簡略的なフライバック回路と説明では、クランプ回路という非常に一般的な改良に触れませんでした。スイッチングFETにかかる電圧は、入力巻き線の静電容量と漏れインダクタンスによって追加される電圧ストレスである出力電圧の反射(Vout×巻き線比N)に、単純な入力電圧を加算した値より遥に大きくなります。

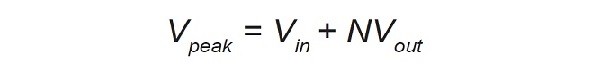

簡略的には、

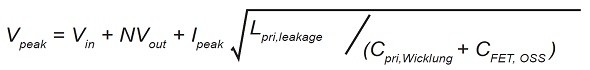

実際には、

この設計例では、FETのピーク電圧スパイクは簡略的な算出で19Vがワーストケースになりますが、例えば100pFの寄生静電容量と10nHの漏れインダクタンスが作用すると、実際のピーク電圧は32V近くになります。つまり、たとえ最大入力電圧がわずか14Vでも、実際には30V定格のFETではもちこたえることができません。

この問題に対する解決策は、静電容量と漏れインダクタンスにより誘発される電圧を低減するために、一次側と平行にスナバネットワークを追加することです。このスナバ、つまり「クランプ」ネットワークは、漏れインダクタンスに蓄積されたエネルギーを消散し、スイッチングFETのストレスを低減します。

クランプ回路は、スイッチング過電圧のエネルギーをそれなりに吸収しますが、発生自体を止めることはできません。そのエネルギーは、クランプ回路、スイッチングFET、トランスの何処へか消散します。最適な消散バランスを見いだすのはかなり困難です。多くのエネルギーがクランプ回路で消散される場合、ダイオードD1は、非常に高温になります。直列抵抗R1を大きくすると、単純にダイオードから抵抗に発熱を転換できます。

クランプ回路の効果を最低限にして、高耐圧のFETを使う場合はEMIが増加します。スイッチングスパイクが減衰されないと、この設計のEMC、伝導および高周波放射の問題は深刻になります。加えて、高電圧スイッチングスパイクは、トランス内での高電流消費の原因となり、結果としてコア温度は上昇し、効率の低下につながり、トランスが過熱状態になる可能性があります。一般的に、たとえFETがピーク電圧に対処できても、クランプ回路はほとんどの場合、常に必要になります。効率向上とEMI低減による恩恵は、クランプ回路の部品コストが追加になることに勝ります。

実用的ヒント

クランプ回路の部品は、可能な限りトランスに近づけて配置する必要があります。スイッチングスパイクは、一次巻き線、R1、C1、D1で構成されるループに大きなピーク電流を流す原因になります。ループに囲まれた領域が小さいと、放射EMIが低減します。

Copyright © ITmedia, Inc. All Rights Reserved.

式1:スイッチングFETのピーク電圧に関する簡略式および実際の計算式

式1:スイッチングFETのピーク電圧に関する簡略式および実際の計算式![<strong>図1:クランプ回路およびスイッチング波形への効果</strong>[クリックで拡大]](https://image.itmedia.co.jp/edn/articles/2406/26/jn20240625dcdc003.jpg)