先見の明が支えたMotorola「MC68000」 PowerPCの陰でロングセラーに:マイクロプロセッサ懐古録(12)(2/4 ページ)

目標はIntelプロセッサの「倍以上の性能」

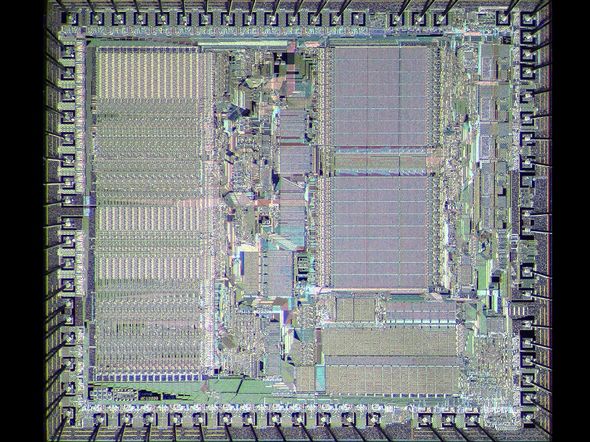

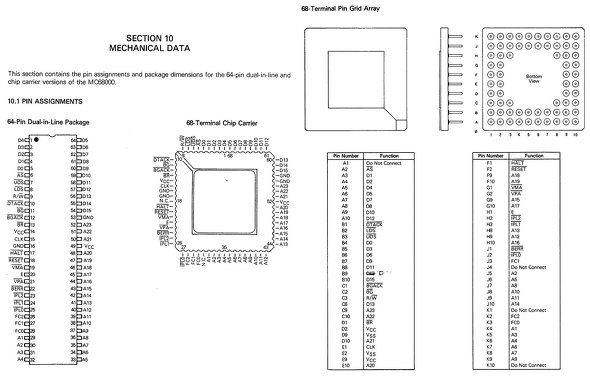

MC68000の開発にあたっての目標は、競合(≒Intel 8086)の倍以上の性能、という事だったそうだ。10%増し程度では顧客に選んでもらうのに十分とはいえない。ハイエンド品では性能2倍、ローエンド品ではコスト半分というのが当時の同社の目標だった。結果から言えば、Intel 8086は、当初出た5MHz品が0.33MIPS程度。8MHz品で0.53MIPS程度だった。一方MC68000は当初4/6/8MHzの製品がリリースされたが、この8MHz品がおおむね1MIPSの性能となっており、「競合の2倍の性能」をほぼ実現できた。トランジスタ数は公式には6万8000個と言われているが、実際にはもう少し多く7万個弱だったらしい(図3)。Motorolaはアドレスバスとデータバスを多重化せずにそのまま出したので、それだけで24+16=40pinを占有。パッケージはまず64pinのDIP、次いで68pinのTCC(Terminal Chip Carrier)と同じく68pinのPGAが提供された(図4)が、この64pinのDIPが問題だった。特にプラスチックパッケージは顧客に"Texas Cockroach"(テキサスゴキブリ)とか呼ばれたらしいのだが、こちらは捻じれなどが発生して大変だったらしい。セラミックパッケージもあったのだが、このパッケージは75米ドルもしたそうで、Motorola的には初期のロットはともかく本格量産で使い続けるのは嫌だったとの事。確かに原価が75米ドルもあがり、しかもそれを最終価格に転嫁しにくいのはあまり好ましかったとは言えないだろう。

日立に救われた製造プロセス

もっと大変だったのは製造プロセスの方だった。MC6800の記事にもちょっとだけ言及したが、1970年代のMotorolaのFabはあまりうまく行っていなかった。Oral History Panelの参加者の一人であるBill Walker氏(当時MotorolaのFabに勤務していた)によれば1970年代後半、同社には3inchのFabが2つあり、片方はNMOS、もう片方はCMOSを製造できたが、どちらも歩留まりが低く、サイクルタイムも長かったらしい。ところがMotorolaは1978年、日立製作所との技術交流を開始する。ここで多くの技術的知見を得て、Motorolaが1980年代初頭に立ち上げた5inchウエハーを使うMOS-8 Fabでは大幅に品質も向上し、生産能力も向上した事で、実際MC68000シリーズの大半を製造する拠点となる。ただ逆に言えばMOS-8が操業を開始するまでは、製造にもちょっと苦労した訳だ。ちなみにMC68000そのものは3.5nm NMOS(MotorolaはHMOSと称していた)で製造されている。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「通信エラー」の原因を追う――搬送機器のコントローラーを修理【前編】

- ARM台頭にルネサス誕生……時代に翻弄され続けた日立「SuperH」

- Ankerがイヤホン用AIチップ、NORフラッシュベースCiM処理

- 「解読不可能」を破る量子コンピュータ――今から始める暗号セキュリティ

- Intelが「Core Series 3」モバイルプロセッサ、エッジ機器向けに

- フェライト(3) ―― 電子部品としてのフェライト

- アルミ電解コンデンサー(1)―― 原理と構造

- AI/HPC用ガラスビア向け 低収縮特性の銅ナノペースト

- SDVとは? 定義や課題、時代に合わせたモビリティDX戦略の重要性

- 次世代車載向けセキュリティコントローラー