サンプリング・オシロを使ったTDNAによるシリアルATA2適合性テスト

コンピュータとストレージ装置間あるいはストレージ装置同士で高速データ転送を行うためのシリアルATAインターフェースの普及が進んでいる。一方で、装置や半導体の設計者は信号の損失やジッター、インピーダンス、リターン損失への注意が必要だ。

パラレルのATA(AT Attachment)技術はほぼ20年間使い続けられてきた。しかし、接続に使われるフラット・ケーブルが装置内部で冷却ファンによるエアー・フローの妨げとなり、設計者はケーブルの引き回し、機構設計に悩まされ続けてきた。さらにパラレル転送方式のため端子数が多く、また低電圧化が進む中で依然として高い信号振幅が必要で、しかも性能はスケーラブルではなかった。このような課題を解決するためパラレルATAストレージ・インターフェースの代替技術としてSATA(Serial ATA)が規格化された。

SATAは転送速度が1.5Gビット/秒または3.0Gビット/秒と、より高速なインターフェースを提供する。パラレルATAに比べ信号電圧レベルはより小さくでき、端子数は少なくなる。加えてはるかに頑丈で細いケーブルが使える。CRC(cyclic redundancy check)を使って、データ、コマンドおよびステータス情報がチェックされるため、SATAは信頼度が高くデータ保全性が確保されている。さらにSATAはソフトウエア的にパラレルATAと完全に互換性があり、物理的なインターフェース層を変更するだけで、パラレルATAから置き換えられる。つまり、デバイス・ドライバの変更は必要ない。

上記の理由からユーザーは低コスト化、性能とスケーラビリティの向上および、より容易な設置が可能という恩恵を得ることができる。しかしながらギガビット/秒を超える高速シリアル・インターフェースであるSATAでは、信号を確実に伝送・受信するために装置設計者は信号の損失(信号レベル)、ジッター、半導体設計者はインピーダンス、リターン損失(Sパラメータ。これについては別掲記事「Sパラメータの基礎」参照)に注意を払うよう、SATA適合性テストの中で義務付けられている。インピーダンスとリターン損失の測定は、これまで周波数領域でのネットワーク解析(FDNA:frequency domain network analysis)で行われてきた。しかし、FDNAにない多くのメリットを持つ、TDR(time domain reflectmetry)を使った時間領域ネットワーク解析(TDNA:time domain network analysis)が最近、新たな測定手法として注目されるようになった。SATA適合性テストにもTDNAが採用されている。ここではTDNAによるSパラメータおよびデターミニスティック・ジッター(DJ)テスト(最大符号間干渉テスト)について紹介する。

SATA IIのSパラメータおよびDJ適合性テスト

SATA1.0aを基に拡張されたSATA IIの仕様*1)では、TDR機能付きのサンプリング・オシロスコープを使ったテストの要求が多い。代表的なテストを以下に示す。

ケーブルおよびコネクタの時間領域(受動物理層)テスト:

a.嵌合コネクタの差動インピーダンス100Ω±15%

b.ケーブルの絶対差動インピーダンス100Ω±10%

c.ケーブル・ペアの整合インピーダンス±5Ω

d.同相インピーダンス25Ω〜40Ω

e.最大立ち上り時間(35ps入力) 85ps(20〜80%)

f.最大符号間干渉50ps

g.最大ペア間スキュー10ps

トランスミッタおよびレシーバの時間領域テスト:

a.差動インピーダンス100Ω±15%

b.シングルエンド(同相)インピーダンス>40Ω

c.差動出力電圧および電圧不均衡

d.立ち上り/降下時間および不均衡

e.差動スキュー

ケーブルおよびコネクタ(受動物理層)の周波数領域テスト:

a.ケーブルの最大挿入損失が−6dB(10MHz〜4.5GHz、内部シングル・レーン*2)

b.最大クロストークが−26dB(10MHz〜4.5GHz、内部シングル・レーン)

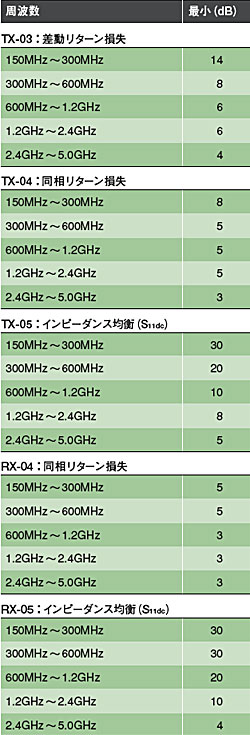

トランスミッタおよびレシーバの周波数領域テスト(表1):

a.トランスミッタ(Tx)/レシーバ(Rx)差動リターン損失

b.Rx/Tx同相リターン損失

c.Rx/Txインピーダンス均衡(差動−同相変換)

SATA IIの周波数領域テスト

SATA IIの仕様では、すべての時間領域テストについては十分に検証されており、詳細が説明されている。そこでここでは、まず周波数領域テストについて説明し、その後に最大符号間干渉テストについて紹介する。

多くの周波数領域テストでは、VNA(vector network analyzer)か後処理ソフトウエアを使用したTDRのうち、いずれかを選択できる。ここでは、後処理ソフトウエアを使用したTDRについて説明する。

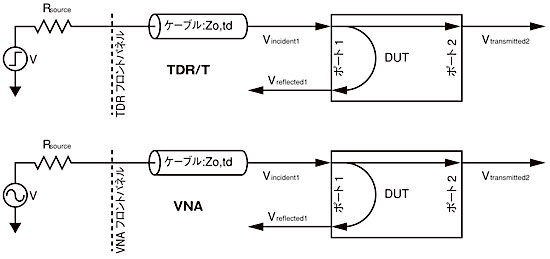

TDNAは、米国標準技術局および米国内外のさまざまな研究機関*3)、*4)などにより詳細に研究され、これに対応した数多くの商品が開発されてきた。概念的には、VNAで行うFDNAとTDNAには類似性がある(図1)。

主な違いは、TDNAで広帯域のステップ波形発生器を用い、VNAでは正弦波発生器を使う点である。これに加えて、TDNAは過渡測定(すべての遷移を観測可能)だが、FDNAは定常状態測定になる。つまり、すべての遷移をひとまとめにし、狭帯域フィルタを適用してノイズの影響を最小限にした状態で、単一周波数で測定する。

VNAは、マイクロ波を考慮して設計されており、マイクロ波フィルタやミキサーの設計などに用いる。広いダイナミック・レンジが必要であるため、ショート・オープン・ロード・スルー(SOLT)、スルー・リフレクト・ライン(TRL)などの高度な校正手順が開発された。また、VNA対応の機器は、使いやすさではなく、ダイナミック・レンジが非常に広いことを前提に設計されている。マイクロ波設計では周波数領域を扱うため、マイクロ波の設計者にとってはFDNAの方がわかりやすい方法となっている。しかし、FDNAの精度を高めている校正手順は同時に、機器の使いづらさや、必要なテストに時間がかかる原因にもなっている。特に製造ラインにおけるテストが関係する場合は、これらが大きな問題となる。

TDNAは、TDR技術の拡張として開発された。TDRは、マイクロ波設計者よりもデジタル回路設計者にとって直観的なものであるため、TDRからSパラメータ・データへの変換は、デジタル回路設計者にとっては簡潔な手順である。SOLTやTRLなどの高度な校正をTDNAに適用して精度を向上することもできるが、TDNA測定が難解でわかりにくくなる。これらの較正手順を利用しない場合でも、TDNAのダイナミック・レンジは−50〜−60dBの範囲であり*5)、デジタル回路や信号整合性の一般的な測定では十分な値となっている。TDNAのダイナミック・レンジは、時間領域取得域でのポイント数および平均値の個数を増加することで向上する。平均を取る回数およびポイント数を増やすことは、FDNAでの信号の狭帯域フィルタと同様の効果がある。まとめると、FDNAとTDNAの相関関係は詳細に研究されており*6)、SATA規格では十分に受け入れられている。一般的なTDNAシステムでは大幅にコストが削減されることも併せて、TDNAソリューションは、使いやすく優れたSATA適合性テスト用ソリューションである。

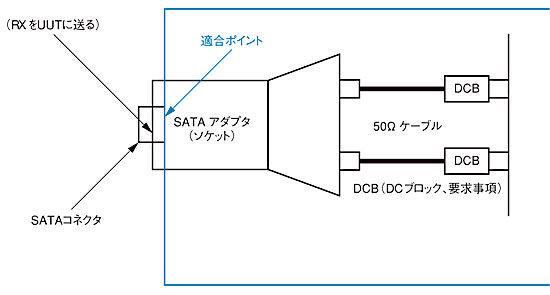

もう1つの重要な点として、SATA IIの適合性テストでは、受動物理層の測定に嵌合コネクタを使うように定義されていることが挙げられる。適合性テスト・ポイントでは、ボード上に接続されたコネクタを測定系から除外する必要がある(図2)。VNAでこれを行うことは不可能ではないが、ただでさえ複雑なVNAでの測定がさらに複雑になる。同時に、TDNAでは、校正が簡単(ショート、オープン、スルーのいずれかの基準だけで実行できる)で、SATAソケットを非常に簡単に除外できるため、この点でも利点がある。つまり、フィクスチャを除外することで、VNAの精度面の利点はあまり意味がなくなった*7)。一方で、TDNAの使いやすさや高いスループットといった利点は変わらないため、TDNAはSATA IIの適合性テストとしてより有効な手法だといえる。

特定周波数領域のSATAテスト

以下の機器を使ってTDNAによる特定周波数領域でのSATAテストを実行した。

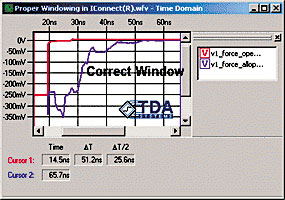

Tektronix社のサンプリング・オシロスコープ「TDS8200型」差動送信実行用の2台のTDRサンプリング・モジュール「80E04型」(または80E04型1台と非TDRサンプリング・モジュール「80E03型」1台)Tektronix社のIConnect TDRおよびVNAソフトウエア。Sパラメータ・テストだけを実行する場合は、ICon-nectのSパラメータおよびZライン(80SSPAR)だけで十分だが、最大ISIテストを実行する場合はフル機能のIConnect(80SICON)が必要長さが同一のSMAケーブルのセット2個のSATA II受動テスト・フィクスチャ TDNA測定を実行する場合は、UUT(unit under test)/DUT(device under test)に対応するすべての遷移を取得域に含めることが重要である(図3)。これにより、過渡時間領域測定を定常状態Sパラメータ測定に正しく変換することができる。取得域が狭すぎると、低周波エラーが発生する。広すぎると、測定のダイナミック・レンジが必要以上に縮小される。また、測定の反射エッジを時間領域取得域に含め、入射エッジを取得域から除外する必要がある。

アクティブ・デバイス(ディスク・ドライブのトランスミッタおよびレシーバ)の測定では、デバイスがAC結合の場合は、前述の手順を使ってテストを直接実行できる。デバイスがDC結合の場合は、テスト中はデバイスをスリープ・モードにしておく必要がある。デバイスをスリープ・モードにできない場合は、テスト時にコンデンサを使ってDCをカットし、デバイスのビーコンをTDR測定から除外する。

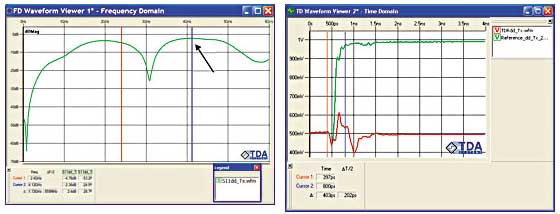

アクティブ・デバイスでリターン損失(Sdd11)を測定するには、適合性テスト・ポイントでは差動基準、DUTからの差動応答が必要である。差動基準は、テスト対象ボード上の専用トレースなどを用いてオープン・エンド反射を取得する。オープン・エンド反射は、トレース長はDUTトレースと同一だが、SATAコネクタに接続されていない(これにより、テストが適合性テスト・ポイントで実行される)場合の反射である。そして、オシロが差動モードで動作している状態で正と負の電圧チャンネル間の差を取得する。DUT差動応答は、オンチップの終端抵抗を有効にするため、デバイスの電源が入った状態で取得する。図4に、ディスク・ドライブのトランスミッタの差動リターン損失測定結果の例を示す。レシーバの測定も、全く同一の方法で実行できる。

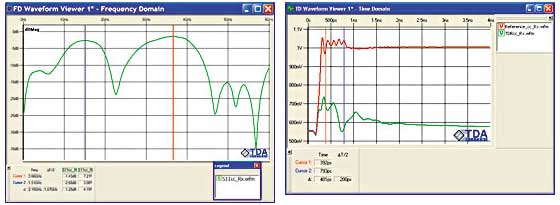

同相測定の場合は、同相基準および応答のTDR波形が必要である。同相基準は、オシロが同相刺激(Stimulus)に設定されている際、オシロでの正と負の電圧チャンネルの和として、SATAテスト対象ボード上の同一の基準オープン・トレースを使って取得する。図5に、ハードディスクのレシーバでこの測定を行った結果を示す。トランスミッタの測定も、同一の方法で実行する。

インピーダンス均衡(混在モードのリターン損失Sdc11)は、同相刺激が有効で、基準波形が2つのチャンネルの電圧の合計である状態で測定する。一方で、応答は2つのチャンネル間の差になる。理想的なインピーダンス均衡の場合は、時間領域での2つのチャンネル間の差は0Vになる。従って、差が生じていれば不均衡が明確に示される。その場合、データを周波数領域に変換し、Sdc11として表示できる(図6)。

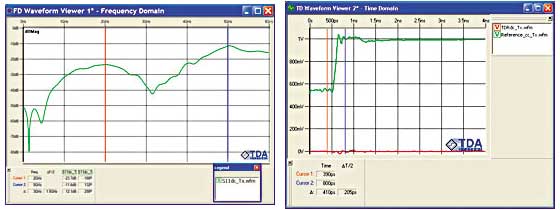

受動物理層では、挿入損失(Sdd21)と周波数領域のクロストーク(Sdd21の別形態)も、IConnectを使用して測定できる。テスト仕様では、内部メディアの場合、挿入損失が4.5GHzまでで最大−6dB、クロストークが4.5GHzで最大−26dBとなっている。すべてのテストは、TDS8200型を完全差動モードで使って実行している。つまり、両方のソースを同時に有効にしている。特にクロストーク測定では、完全差動測定を有効活用でき、TDNAでの測定が大幅に簡潔になる。差動基準は、オシロが同相刺激に設定されている場合のオシロでの正と負の電圧チャンネルの差として、多くのSATA受動テスト対象ボードに見られるスルー基準トレースを使って取得できる。図7に、SATAケーブル・アセンブリの挿入損失の測定結果を示す。図8には、周波数領域のクロストーク測定の結果を示す。これらの結果はいずれも、DUTが仕様に準拠していることを示している。デバイスの挿入損失は4.5GHz まで−3.12dB、クロストークは−37.1dBにとどまっている。

最大ISI測定

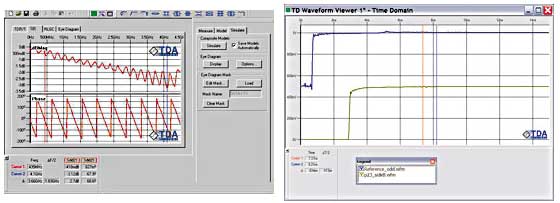

IConnect(80SICON)を使って効果的に実行できる別の測定例として、ケーブル・アセンブリなどの受動物理層デバイスでの最大ISIテストがある。受動物理層でのDJの特性上、IConnectで差動送信測定結果をSATA IIの速度でのアイパターン図に変換し、ピーク間のDJ(最大ISI)を測定することができる。この測定でも、フィクスチャを簡単に除外できるため、IConnectを使うことでとても効率的に測定が行える。

SATA IIの仕様では、以下のように規定されている。この構成では、2X cal/基準トレース(すべてのSMAケーブル・ブレークアウト・ボードにある)全体で、ケーブル・フィクスチャ固有のランダムシッター(RJ)およびDJを測定して記録する。

IConnectでは、Sパラメータ測定の場合と同様に、テスト対象フィクスチャのジッターが測定の一部として自動的にすべて除外される。

これに続いて、以下のように規定されている。

差動パターン・ソースをテスト対象フィクスチャの入力で接続する。フィクスチャを経由してローン・ビット・パターンを3.0Gビット/秒で生成する。

ローン・ビット・パターンは、0011 0110 1111 0100 0010 0011 0110 1111 0100 0010と定義されている。このパターンは、IConnectでは標準構成に含まれており、*.mts(マスク)SATA-IIファイルとして読み込むことができる。JMD(jitter measurement device)を使って、ケーブル終端で挿入されるDJを評価する。テスト対象フィクスチャおよび刺激システムのDJへの影響を考慮しなければならない。 (テスト対象システムに起因する)入射DJは結果から除外できないため、この測定を実行する場合は、高品質(低ジッター)フィクスチャおよび刺激システムを使用することが重要である。 IConnectではこれらの影響を簡単に除外できる。ここでも、フィクスチャによる測定全体への影響を考慮する必要はほとんどない。

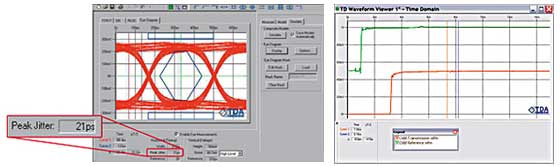

図9に、最大ISIの測定結果を示す。このDUTのピーク間ジッターは21psとなっており、SATA IIの最大ISI要件を十分に満たしている。最大ISI測定では、後処理ソフトウエアを追加することで、SATA IIのケーブル・アセンブリの全テストをTDRプラットフォームで実行できる。

Sパラメータの基礎

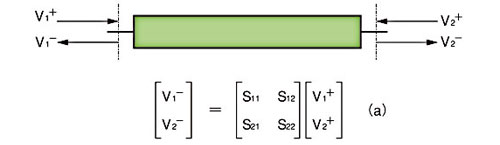

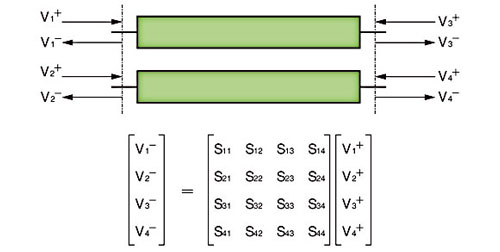

Sパラメータは、各ポートでの入射波および反射(送信)波で定義される。各Sijパラメータは、ポートjでの反射波とポートiでの入射波の比率を示す(図A)。

反射は、一般的には散乱と呼ばれる。送信出力が1/2│Vi+│2で与えられる場合、各ポートでの電圧はV=V++V−、電流はI=I+ +I− で定義される。相互結合(相互接続など)の場合は、散乱行列は対称(S21=S12)になる(図A(a))。

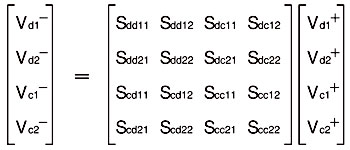

4ポートの場合は、2ポートの定義をそのまま拡張するが、概念はさらに複雑になる(図B)。

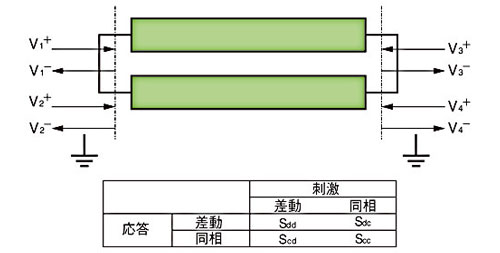

ここで重要な点は、差動および同相の測定である。差動測定ではラインとラインの差を測定し、同相測定ではまとめたラインからグラウンドまでを測定する。実際には、刺激とそれに対する応答の種類により、対象のSパラメータの種類が定義される。差動刺激と差動応答の場合は、Sパラメータの差動象限が定義される。同相刺激と同相応答の場合は、同相象限が定義される。差動刺激と同相応答の場合は、差動−同相変換混在象限が定義される。同相刺激と差動応答の場合は、同相−差動変換混在象限が定義される(図C)。

結果のパラメータの行列は次のようになる。

各Sパラメータは、デジタル回路のさまざまな要素に関係する。Sパラメータの差動象限は、帯域およびBER/ジッターの直接劣化に関係する。同相象限は、スキューおよびグラウンド・バウンスの問題に関係する。混在象限は、EM干渉(EMI、差動−同相変換)およびEM耐性(EMS、同相−差動変換)に関係する。ただし、EMIおよびEMSの原因を調べる場合は、同一データの時間領域表示の方がより直観的な結果を得られる。一方、クロストークは挿入損失(S21)で示される。ただし、入力から出力への直接接続がないライン間の挿入損失になる。

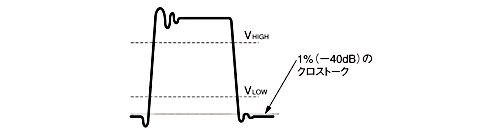

デジタル回路設計では、相互接続チャンネルの周波数領域での作用を特定する必要があること、およびSATAなどの多くの規格で適合性テストが要求されることから、Sパラメータ測定(TDNAまたはFDNA)が必要になる。適合性テストでは、一般に測定値が約−30dB (SATAの場合は周波数領域クロストークが−26dB)に制限される。また、周波数領域での−40dBはデジタル信号の全振幅の約1%に相当するため、チャンネル解析では−40dB以上の測定能力は要求されない(図D)。

脚注:

※1…Serial ATA II: Electrical Specification. Revision 1.0, 26-May 2004

※2…外部シングル・レーンおよびマルチ・レーンのメディアの仕様は、内部シングル・レーンの仕様とは若干異なる。ただし、主なSATA用途では、内部シングル・レーン・メディアの方が重要である。

※3…L.A. Hayden, V.K. Tripathi, “Calibration Methods for Time Domain Network Analysis”―IEEE Transactions on Microwave Theory and Techniques, Vol. 41, No. 3, March 1993, pp. 415-421

※4…T.Dhaene, L. Martens, D. De Zutter,“Calibration and Normalization of Time Domain Network Analyzer Measurements,”―IEEE Transactions on Microwave Theory and Techniques, Vol. 42, No. 4, April 1994, pp. 580-589

※5…T. Custer, “Dynamic Range Determination and S-Parameter Accuracy Validation for High Frequency Time Domain Network Analyzer(TDNA)Measurements,“―Samtec, Inc. technical note, 2005

※6…Cherry Wakayama, Jeff Loyer, “Correlation between VNA and TDR/TDT Extracted S-Parameters up to 20 GHz,“―Intel Corporation white paper, 2005

※7…“Effects of Measurement Fixtures of S-Parameters Compliance Testing of Infiniband Cable Assemblies,“―Tektronix Application Note 85W-18993-0.

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

表1 Tx/Rx周波数領域テストの詳細

表1 Tx/Rx周波数領域テストの詳細  図1 TDRベースのTDNAシステムとVNAの概念図

図1 TDRベースのTDNAシステムとVNAの概念図 図2 SATAIIの適合性テスト 適合性テスト・ポイントは、受動物理層の測定に嵌合コネクタを使うように定義されている。

図2 SATAIIの適合性テスト 適合性テスト・ポイントは、受動物理層の測定に嵌合コネクタを使うように定義されている。 図3 SパラメータをTDNA手法で取得するための正しい取得域 取得域には、DUTに対応するすべての遷移を含める必要がある。

図3 SパラメータをTDNA手法で取得するための正しい取得域 取得域には、DUTに対応するすべての遷移を含める必要がある。 図4 差動トランスミッタのリターン損失測定結果(左)と、挿入損失の取得に要求される時間領域波形(右) 4.12GHzで−2.4dBを示しているため(矢印)、デバイスは仕様に準拠していない。

図4 差動トランスミッタのリターン損失測定結果(左)と、挿入損失の取得に要求される時間領域波形(右) 4.12GHzで−2.4dBを示しているため(矢印)、デバイスは仕様に準拠していない。 図5 同相リターン損失の測定結果(左)と、要求される時間領域波形(右) デバイスは仕様に準拠している。

図5 同相リターン損失の測定結果(左)と、要求される時間領域波形(右) デバイスは仕様に準拠している。 図6 インピーダンス均衡(混在モードのリターン損失Sdc11)の測定結果(左)と、測定損失の取得に要求される時間領域波形(右) デバイスは仕様に準拠している。

図6 インピーダンス均衡(混在モードのリターン損失Sdc11)の測定結果(左)と、測定損失の取得に要求される時間領域波形(右) デバイスは仕様に準拠している。 図7 挿入損失の測定結果(左)と、挿入損失の取得に要求される時間領域波形(右)。

図7 挿入損失の測定結果(左)と、挿入損失の取得に要求される時間領域波形(右)。 図8 周波数領域のクロストーク測定結果(左)と、要求される時間領域のクロストーク波形(右)。

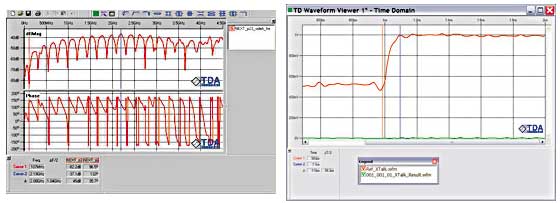

図8 周波数領域のクロストーク測定結果(左)と、要求される時間領域のクロストーク波形(右)。 図9 最大ISIの測定結果(左、赤枠内)および要求される時間領域波形(右)。

図9 最大ISIの測定結果(左、赤枠内)および要求される時間領域波形(右)。

図A Sijパラメータは、ポートjでの反射波とポートiでの入射波の比率

図A Sijパラメータは、ポートjでの反射波とポートiでの入射波の比率  図B 4ポートの概念 この場合はSパラメータ行列の計算に関係する電圧および電流の値が多くなり、行列そのものの次元は4×4になる。

図B 4ポートの概念 この場合はSパラメータ行列の計算に関係する電圧および電流の値が多くなり、行列そのものの次元は4×4になる。  図C 応答と刺激の関係 差動刺激と差動応答の場合は、Sパラメータの差動象限が定義される。同相刺激と同相応答の場合は、同相象限が定義される。差動刺激と同相応答の場合は、差動−同相変換混在象限が定義される。同相刺激と差動応答の場合は、同相−差動変換混在象限が定義される。

図C 応答と刺激の関係 差動刺激と差動応答の場合は、Sパラメータの差動象限が定義される。同相刺激と同相応答の場合は、同相象限が定義される。差動刺激と同相応答の場合は、差動−同相変換混在象限が定義される。同相刺激と差動応答の場合は、同相−差動変換混在象限が定義される。  図D 周波数領域での−40dBはデジタル信号の全振幅の約1%に相当 このため相互接続チャンネル解析では−40dB以上の測定能力は要求されない。

図D 周波数領域での−40dBはデジタル信号の全振幅の約1%に相当 このため相互接続チャンネル解析では−40dB以上の測定能力は要求されない。