チップ内ばらつきを考慮したLSI設計手法(2/3 ページ)

チップ内ばらつきのモデル化

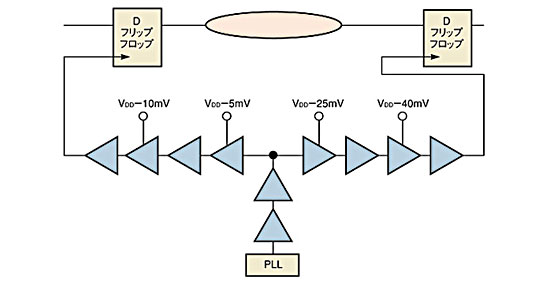

デジタル回路の設計においては、一般に、極端なプロセス条件を想定して回路のタイミングシミュレーションを行う。この解析では通常、どの条件においてもゲートまたは配線性能にミスマッチはないとし、セルがワーストケースまたはベストケースであると見なす。しかし、この仮定はもはや有効ではない。ディープサブミクロンプロセスが複雑になるに連れ、同一チップ上の素子/配線間の特性ばらつきはもはや無視できないものとなった。クロック信号ラインにおいては、この影響が顕著である。論理的に独立したフリップフロップのクロック遅延が大きくなったり小さくなったりすることにより、目標とする性能が達成できない場合がある。最悪の場合、セットアップ/ホールドエラーが生じ、デバイスが正常に動作しない可能性もある(図1)。

そこで、設計フローをよく検討し、このような問題を回避することが必要になる。ここではチップ内ばらつきの発生原因を、ランダムな要素と決定的な要素に分けて考える。ランダムな要素には、例えばゲート酸化膜の厚さ、イオン注入量、金属配線または絶縁膜厚のばらつきなどが該当する。一方の決定的な要素とは、ウェーハ上の位置や周囲のパターンの性質から予測できるばらつきのことで、近接効果、密度、および素子間の相対的距離に関連するものである。例としては、ゲート長やゲート幅、配線幅のばらつきなどが挙げられる。その他の決定的なばらつきとしては、製造装置ごとに特有な放射状または線形の勾配によるものがある。

これらの影響のモデル化には、スタティックなタイミング解析時にタイミングディレーティング係数を用いることにより、あらゆるゲート/配線上の動作速度の上昇/低下を全体に対する割合で表すことで行う。セルごと、または配線単位のランダムなばらつきおよび決定的なばらつきの合計が、全体のばらつきとなる。

電圧とIRドロップのモデリング

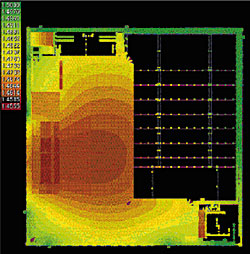

従来は、エレクトロマイグレーション耐性を保証し、全体として目標とするIRドロップを許容範囲内に抑えるためにIRドロップ解析を行っていた。しかし、複雑なプロセスでは、IRドロップがトランジスタ性能に深刻な影響を及ぼすため、スタティックなタイミング解析時にこれを考慮する必要がある。図1において、初段フリップフロップのクロックツリーバッファのIRドロップが許容範囲の最大値に近く、最終段フリップフロップのクロックツリーバッファのIRドロップが許容範囲の最小値に近い場合は、それぞれのフリップフロップにおける2つのクロックの到達時間にかなりの差が生じる。このずれ(スキュー)が大きすぎる場合は、セットアップ/ホールドエラーが生じる。IRドロップがタイミングに及ぼす影響に対処するには、影響を受けるセルに対して、電源電圧の関数として遅延値を一律に決めるkファクタを用いた方法とは異なる手法を確立する必要がある(図2)。

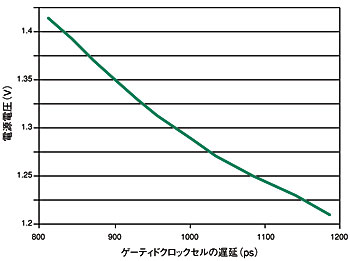

タイミングに対するIRドロップの影響を定量化するには、クロックバッファやインバータ、クロックゲーティングセルを含むライブラリのスタンダードセルに対してSPICEシミュレーションを行うとよい。プロセス、電圧、温度の変動に対して、IRドロップが電源電圧の5〜10%の範囲内であれば、各セルの遅延の増加は、130nm〜90nmプロセスの場合、電源電圧の低下に対してほぼ線形となる。図3に示したのは、標準の電源電圧が1.35Vの場合のワーストケースでのゲーティドクロックセルの遅延と電源電圧の関係である。ここで、電源電圧の低下に対する遅延の値がほぼ線形であることに注意されたい。これは、ばらつきについて考慮しなければならない範囲では、遅延の増加は電圧に対する線形関数として表せるということだ。従って、この特性を考慮すれば、IRドロップによって発生する各セルの遅延の増加率を概算することができる。

ただし、曲線の勾配は各スタンダードセルごとに異なる可能性がある。あるライブラリ内の各セルの遅延値が同一の勾配を持つのなら、kファクタを用いた方法でよいことになる。しかし、実際にはそれでは正確な結果は得られない。

各セルに対するディレーティング係数を決定したら、IRドロップ解析ツールからの出力結果とSPICEシミュレーションから得られたディレーティング係数を組み合わせるスクリプトを記述するとよい。それにより、IRドロップツールからの出力を利用して、各インスタンスのタイミングディレーティングを作成することができる。これにより、各セルの実際の電源電圧値を考慮した、より現実的なスタティックタイミング解析が可能となる。

Copyright © ITmedia, Inc. All Rights Reserved.

図1 クロック信号ラインにおけるばらつきの例 IRドロップの差が大きすぎると、クロックスキューが生じ、セットアップ/ホールドエラーが発生する。

図1 クロック信号ラインにおけるばらつきの例 IRドロップの差が大きすぎると、クロックスキューが生じ、セットアップ/ホールドエラーが発生する。 図2 チップ上のIRドロップの分布 ネットリスト内の個々のセルに対する遅延値を調整する。

図2 チップ上のIRドロップの分布 ネットリスト内の個々のセルに対する遅延値を調整する。 図3 遅延と電源電圧の関係 遅延と電源電圧の関係は、ほぼ線形である

図3 遅延と電源電圧の関係 遅延と電源電圧の関係は、ほぼ線形である