低価格FPGA開発キットの実用性を探る:主要4製品の使い勝手を実践検証!(2/5 ページ)

ProASIC Plusスタータキット――Actel社

Actel社のProASIC Plusスタータキット(価格は約285米ドル)には、134mm×125mmの評価ボードが含まれている。その評価ボードには、Actel社の30万ゲートのProASIC PlusファミリFPGA「APA300」が搭載されており、このFPGAを取り囲む多数の端子ヘッダーは同FPGAの入出力として利用できるようになっている。そのほか、ユーザーが同FPGAからの出力として使用できる8個のLEDと、同FPGAへの入力として使用できる5個のプッシュボタンが実装されている。

高密度な26端子ヘッダーは、ProASIC Plusスタータキットに付属する「FlashPro Liteプログラマ」との接続に使用する。FlashPro Liteプログラマとパソコンはパラレルポートケーブルで接続する。AC-DCアダプタの供給電圧は直流の9Vであり、この直流電圧は2個のレギュレータによって2.5〜3.3Vまで降圧される。FPGAのコア部分は2.5Vで動作し、I/Oブロックの電源は2.5Vか3.3Vのどちらかをジャンパで選択できる。

ユーザーガイドや回路図、設計ファイルを収録したスタータキットCD-ROMと、紙版の「User's Guide&Tutorial」が付属している。そのほか、統合開発環境「Libero IDE」とデバッギング用のソフトウエア「Logic Navigator」のインストールCD-ROMが付属している。便利なことに、FPGAチップには評価ボードに実装されたハードウエアのテスト用プログラムがあらかじめ書き込まれている。

ProASIC Plusの内部構造

ProASIC Plusファミリ製品は、再書き込みを可能にする「リプログラマブルフラッシュテクノロジ」を採用している。それにより、外部にコンフィグレーション用のメモリーとサポートロジックを用意する必要がなく、設計が容易ですぐに使用できる。

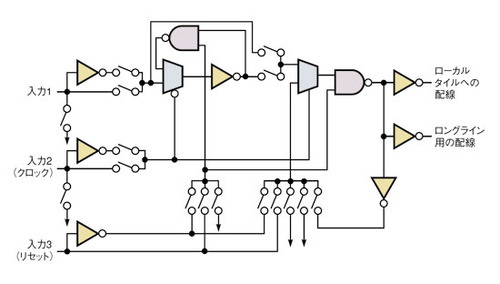

ProASIC Plusは、アーキテクチャとして「sea-of-tiles(タイルの海)」構造を採用している。これは、基本セル(タイル)を縦横に敷き詰め、デュアルポートSRAMブロックとI/Oブロックを周囲に配置する構造である。このファミリ製品の1つであるAPA300は8192個のタイルを備える。それらタイルはDフリップフロップのような3入力1出力のロジック回路として構成できる(図1)。それらをチップ内の配線リソースを使用して接続する。

配線方式としては、ローカル、ロングライン、超ロングライン、グローバルのうちいずれかを選択できる。当然ローカル配線が最速であり、9タイルのアレイ内で1タイルの出力を残り8タイルの入力に接続することが可能である。ロングラインの配線はデバイス内を縦横に走り、1個、2個、または4個のタイルを接続できる。同じように超ロングラインの配線もデバイスをグリッド状に覆い、ファンアウトの大きい信号線を形成する。グローバル配線は、一般にクロックとリセット信号の分配に適している。

ほかの特徴としては、アナログPLL(phase locked loop)と0.25ns単位で調整可能な遅延ライン、直交位相シフター、クロック逓倍器/分周器から構成される2つのクロック調整ブロックや、プログラマブルシュミットトリガー入力端子などがある。加えて、決められた範囲内のタイルを接続するクロックツリーネットワークにより、最大32種類のクロックを効率的に分配できる。

Libero IDEのインストール

Libero IDEを使用すれば、経験に関係なくすべてのユーザーが設計フローに沿って容易に作業を進められる。このソフトウエアは、Windows 2000 Pro SP4/XP Pro SP2やSolaris、Red Hat Linux上で動作する。ウェブサイトでユーザー登録すると、Gold IDEエディションのライセンスファイルが電子メールで送られてくるので、それを使ってパソコンへのインストールを行う。また、このライセンスファイルにより「Synplicity Identify AE(Actel社エディション)」のソフトウエアコンポーネントが利用できるようになる。

Libero IDEを起動すると、ウェブサイトへの自動アクセスが行われ、アップデートの有無がチェックされる。筆者が確認したときは、バージョン7.2とその更新用の差分ファイルであるサービスパック2が提供されていた。アップデートとしてダウンロード可能なのはフルインストール版であるため、以前のバージョンをアンインストールするか、別のディレクトリに改めてインストールする必要がある。従って、CD-ROMを使用せずに、最初からウェブで入手可能なパッケージを使用してもよいだろう。Libero IDEを使い始める前に、「Quick Start Guide」をダウンロードして目を通しておくことをお勧めする。

簡便な開発フロー

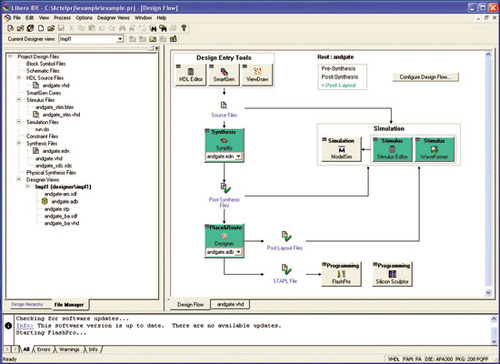

チュートリアル(ProASIC PLUS Starter Kit User's Guide&Tutorial)に従えば、VHDLで記述したANDゲートのコードのコンパイルからステップバイステップで開発作業を実践できる(図2)。VHDLやVerilogなどのハードウエア記述言語になじみのないユーザーには、入門者向けガイドがウェブ上にたくさんあるので、一読しておくことを勧める(Verilogについては参考文献*3)が、VHDLについては*4)が参考になる)。

こうしたエントリレベルの設計ツールの能力は、16ビットカウンタのような単純な回路を合成してみればすぐに分かる。回路図を入力する方法の場合、フリップフロップや、そのほかのロジック回路、配線などを16ビット分作図しなければならない。しかしLibero IDEを使用すれば、標準的なテキストファイル(VHDL/Verilogコード)内のパラメータを変更するだけで任意のビット長のカウンタを作成できる。

環境によっては、操作が分からず混乱してしまう場合もあるが、Libero IDEであれば初心者でも簡単に作業を進められる。かといって、すべてががんじがらめに縛られているわけでもないので、それなりの自由度が必要となる実使用にも十分に対応できる。

ただし、残念なことにスタートアップキットのチュートリアルにタイプミスがある(3行目の「iee」は「ieee」でなければならない)。そのため、VHDLコードの最初のコンパイルは失敗に終わる。この誤りを修正したら、次のステップでは米SynaptiCAD社の「Wave Former Lite」を実行する。このツールは2500米ドルもする「WaveFormer Pro」の簡易版だが、グラフィカルな入力操作によってテストデータを生成できる。なお、テストベンチデータはLibero IDEのHDLエディタで直接作成してもよい。

Libero IDEのチュートリアルはバージョン2.3 SP2に基づいて作成されている。サンプルファイルのandgate.vhdを右クリックすると、チュートリアルのそれとは異なるオプションが表示されるので注意が必要だ。テストデータのファイルとandgate.vhdを関連付ける[Run Presynthesis Simulation]オプションを選択すると、米Mentor Graphics社製「ModelSim」のActel社バージョンが起動し、テストデータがコンパイルされる。画面には、Wave Former Liteで作成した入力A/Bの波形のほか、シミュレータによる出力波形が表示される。

シミュレータにより正常な動作を確認したら、次に「Synplify」を使用してEDIF(electronic design interchange format)ネットリストファイルを生成する。この出力ファイルはLibero IDEによってシームレスにVHDLネットリストに変換され、ファイルマネジャウィンドウに表示される。何らかのエラーが発生した場合には、Synplifyでファイルを編集することにより、その変更内容がLibero IDEにバックアノテートされる。ModelSimによって合成後シミュレーションを実行すると、伝搬遅延を含む出力波形が表示される。

設計をデバイスに実装するには「Designer」を実行し、デバイスとそのパッケージを選択してから[Compile]ボタンをクリックする。コンパイルに成功するとこのボタンが緑色に変わる。次に「Pin Editor」内でANDゲートの端子をドラッグ&ドロップによって割り当て、[Layout and Back-Annotate]を実行すると、Libero IDEによってandgate.ahbというファイルが生成される。なお、ModelSimを使用してもう一度タイミング特性のシミュレーションを行ってからデバイスをプログラムすることも可能である。

Designer内の[Programming File]ボタンをクリックすると「STAPL(standard test and programming language)」ファイルが生成され、Libero IDEのファイルマネジャウィンドウの[Implementation Files]セクションにそれが表示される。デバイスをプログラムするまでのこれらすべてのプロセスは、Libero IDEの設計フローウィンドウで追跡できる。

APA300にプログラムを書き込むソフトウエア「FlashPro 4.2」にも、旧バージョン向けに書かれたマニュアルの説明と若干異なる部分がある。しかし、作業ステップ自体は明確で分かりやすい。

ここまでの作業を終えたら、評価ボードのスイッチ1と2を押す。それによりLED1が点灯すれば、今回のVHDLサンプルのコンパイルとプログラミングが正しく行われたことが確認できる。

VHDLによる設計手法を用いず、「ViewDraw」を使用して回路図入力によって設計を行う場合には、ある程度の労力を要する。なぜなら、Mentor社のウェブサイトで提供されているViewDrawのチュートリアルは十分なものとはいえないからだ。とはいえ、主な情報はViewDrawディレクトリに格納されているユーザーガイドから入手できる。ViewDrawは十分直感的に操作可能であるため、簡単なサンプルを作成してその出力をLEDに関連付けることができるようになるころには、設計フロープロセスが簡単に思えてくることだろう。

高度な設計のための拡張性

Actel社の販売/マーケティング担当シニアバイスプレジデントであるDennis Kish氏は、新しく同社のユーザーになろうとする人には、昨年発表した「ProASIC3/E」ファミリを勧めている。このファミリのシステムゲート数は3万〜300万で、搭載されているロジック数は類似製品のProASIC Plusデバイスよりも約25%多く、動作速度は約2倍である。また、ホットスワップ(活電挿抜)が可能なI/O構成となっているため、ボード設計の複雑さが大幅に軽減される。

Kish氏は、システム管理などの用途向けには、A-Dコンバータなどのアナログ機能を統合した「Fusion PSC(programmable system chip)」を勧める。また、携帯機器などの省電力アプリケーションをターゲットとした「Igloo」ファミリのサンプル出荷も2007年第1四半期に開始される予定だという。この新ファミリはProASIC3/Eと互換性があるだけでなく、すべてのステート情報を保持しつつデバイスをトライステートにできる「FlashFreeze」という省電力入力端子を備えている。最小サイズの「AGL030」であれば、この方法で消費電力を約5μWにまで低減できる。

Actel社は、英ARM社のARM7コアのライセンスを取得している唯一のFPGAベンダーである。ARM社の開発ツール「RealView」のActel社バージョンを低価格で提供していることからも、両社の結び付きの固さがうかがえる。「当社のツールには、これからFPGAの設計を始める人にも使いやすいように最適化されたソフトウエアと、パワーユーザーのためのオプションやショートカットがすべてそろっている」とKish氏は語る。

脚注

※3…www.verilog.net/docs.html.

※4…www.vhdl.org/comp.lang.vhdl/FAQ1.html#3.

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

図1 ProASICPlusのタイルの内部構造 Actel社のProASICPlusでは、各タイルが3入力1出力のロジックとしての機能を備える。

図1 ProASICPlusのタイルの内部構造 Actel社のProASICPlusでは、各タイルが3入力1出力のロジックとしての機能を備える。 図2 LiberoIDEの操作画面 LiberoIDEでは、ステップバイステップで設計/実装が行える。

図2 LiberoIDEの操作画面 LiberoIDEでは、ステップバイステップで設計/実装が行える。