低価格FPGA開発キットの実用性を探る:主要4製品の使い勝手を実践検証!(4/5 ページ)

CoolRunner-II Design Kit――Xilinx社

Xilinx社は同社のCPLD「Cool Runner-II」向けに、「CoolRunner-II Design Kit」を提供している。49米ドルという低価格で提供されている同開発キットには、2個のCPLDと1.8432MHzの発振回路、電源を搭載し、試作用の十分なエリアを備えた133mm×133mmの評価ボードが付属する。初めて利用する人は、Xilinx社から「Programmable Logic Design Quick Start Handbook」(紙版:約200ページ)を入手して、参考にするとよいだろう。開発キットに付属するCD-ROMにも多数のドキュメントが収録されており、評価ボードの回路図や、TTLをCPLDに置き換える方法が記載されたガイドなども含まれている。

同開発キットの利用に当たっては、無料の設計ソフトウエア「ISE(integrated software nvironment)Web PACK」をXilinx社のウェブサイトからダウンロードするとよい。このソフトウエアにはライセンスファイルも有効期限もなく、すぐに使用できる。Xilinx社製品用のModelSimをインストールしておくのもよいだろう。インストールする際には、有効期限がある完全バージョンと、500行までのコードをデバッグできる無料バージョンのうちどちらかを選択する。

米Digilent社によってビルドされたISE WebPACKには、デバイス書き込み用のJTAG-3パラレルポートアダプタケーブルが付属しているが、ボードの電源は自分で用意しなくてはならない。単3電池を2本使用して作業するか、直流5V〜9Vのアダプタからソケットに電力を供給する。その際、ボードの損傷を防ぐために、電源投入前に電源選択ジャンパの設定が正しいことを確認する必要がある。アダプタを使用すれば許容電圧18Vの2個のレギュレータに電力が供給されるため、この方法が最も安全である。

ジャンパを使用すれば、各CPLDとJTAGチェーンの接続を設定したり、オンボードオシレータや32MHz〜100MHzの外部クロックを供給したりすることが可能である。さらに、2列40端子のコネクタ4個を使用すれば、両方のCPLDからの信号をすべて有効にできる。これらのコネクタはDigilent社が提供する拡張ボードと互換性がある。

評価ボードに実装されている2つのCPLDのうち1つはXC9500シリーズの「XC9572XL」である。このデバイスは、72個のマクロセルと1600個のゲート、72個のレジスタ、34個のI/Oを44端子PQFPにパッケージングした製品だ。3.3Vの電源と5VのI/O用電圧との変換を必要とするアプリケーションに適している。

CoolRunner-IIの内部構造

もう1つの「XC2C256」がCoolRunner-IIシリーズの製品で、256個のマクロセルを備える。このマクロセルは、独自開発のAIM(advanced interconnect matrix)によって相互接続され、16個の機能ブロックに分かれている。各マクロセルは56個の入力を備える論理ブロックで、その積項を機能ブロック内のマクロセルに配線し、共有することができる(図4)。この配置により、配線の柔軟性を最大限に高め、伝達遅延を最小限に抑えることが可能となっている。加えて、使用されていない積項を隣接するマクロセルから借用して積項幅を広げることができる。さらに、同期リセット回路を備えた2〜16倍のプログラマブル分周期のクロックシステムを持つ。設計キットに含まれている144端子のTQFPデバイスには118個のI/Oがあり、約500mVのヒステリシスを持つシュミットトリガー入力を任意に設定できる。

Spartan-3のチュートリアルを参考に

ISE WebPACKを使用するには、紙版のマニュアルを読む、ウェブベースのチュートリアルを参照する、ISE WebPACKのヘルプメニューによって表示できるクイックスタートガイドを参照する、詳細なPDFチュートリアルをダウンロードして読むといった方法がある。VHDLに関しては、CD-ROMに収録されているCPLD向けVHDLチュートリアルや、Digilent社のウェブサイトで提供されているVHDLコードについて説明した5分間の無料ビデオがある。しかし、このボードの構成とプログラム方法について説明したチュートリアルは残念ながら存在しない。

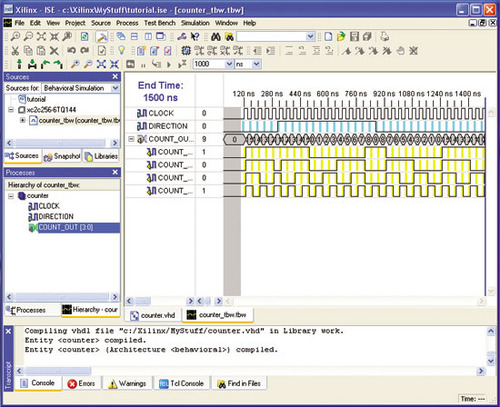

ただし、Xilinx社のFPGA「Spartan-3」の評価ボード向けの「ISE Quick start tutorial」では、アップカウンタ/ダウンカウンタの実装方法やデザインエントリの手順、動作シミュレーションの方法、タイミング制約の入力を分かりやすく説明している。XC2C256の評価ボードを用いてSpartan-3のサンプルを利用する場合、使用できないのは最後のタイミング制約エントリのみである。これは、CPLDでは、FPGAの設計サマリーではなくフィッタレポートを生成するためだ。端子を割り当てるエディタも異なるが、使用方法はヘルプを参照すれば分かるようになっている。タイミングシミュレータでは、直感的に機能を検証できる(図5)。

168ページにも及ぶチュートリアルでは、回路図によるデザインエントリも説明している。ISE WebPACKの[File]タブから[Open Example]メニューを開き、「watch_sc_cr2」のサンプルファイルを開くと、混合モードのマクロ設計、回路図設計、VHDL設計の実装方法を見ることができる。このサンプルはCoolRunner-IIシリーズの「XC2C128」に基づいている。

筆者が試した際、一番難しかったのは、カウンタ設計をダウンロードする前にボード上からテストプログラムを保存することだった。大抵の環境には独立したデバイスへの書き込み専用のインターフェースがあるものだが、ISE WebPACKでは[Processes Window]内の[Generate Programming File/ Configure Device]タブにそれらの機能がある。JTAGジャンパはすべてデフォルトに設定し、プログラミングケーブルを接続してデバイスへの書き込みソフトウエアを起動したら、[Automatically Connect to a Cable & Identify Boundary-Scan Chain]オプションを選択する。これでソフトウエアが両方のデバイスを認識する。

どちらかのデバイスを右クリックすると[Programming]メニューが表示される。Digilent社の「Impact Device Configuration Notes」によれば、ISE WebPACKではデフォルトでJTAG経由のプログラムファイルを生成しない。そのため、[Generate Programming File]を右クリックして[Properties]を選択し、[Create IEEE 1532 Configuration File]ボックスにチェックを入れる必要がある。さらに詳しい情報はXilinx社のウェブサイトで提供されており、そこで無料のCPLDリファレンス設計とコードファイルも入手できる。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

図4 CoolRunner-IIのマクロセル CoolRunner-IIのマクロセルは最大56本の入力に対応する。

図4 CoolRunner-IIのマクロセル CoolRunner-IIのマクロセルは最大56本の入力に対応する。 図5 ISEWebPACKのタイミングシミュレータの画面 タイミングシミュレータインターフェースは直感的に使用できる。

図5 ISEWebPACKのタイミングシミュレータの画面 タイミングシミュレータインターフェースは直感的に使用できる。