低価格FPGA開発キットの実用性を探る:主要4製品の使い勝手を実践検証!(5/5 ページ)

MachXOスタータ評価ボード――Lattice Semiconductor社

最後に取り上げるのは、Lattice Semiconductor社が初心者向けに提供しているMachXOスタータ評価ボードである。この評価ボード(単価は99米ドル)のサイズは85mm×72mmしかなく、さらにそのスペースの大部分は端子ヘッダーとコネクタに使用されている。ボードに実装されたハードウエアは、100端子TQFPのFPGA「LCMXO256C」、33MHzの発振器、各種スイッチ、LED、JTAG接続用ヘッダー、いくつかの電源レギュレータで構成されている。AC-DCアダプタの5V出力がコアの種類に応じて3.3Vまたは1.2Vに降圧される。また、レギュレータを使用してI/Oのレベルを1.25〜3.3Vの範囲で設定できる。初期状態ではすべてのレベルが3.3Vに設定されている。

紙版の「User's Guide」には、評価ボードのハードウエア構成とI/O接続のリストが記載されている。またパソコンのパラレルポートとボードのJTAGヘッダーを接続するispDOWNLOADケーブルとプログラミングガイドが付属している。

ispLEVERのインストール

MachXOスタータ評価ボードには、ソフトウエアは含まれていない。システムの実行に必要な環境「ispLEVER-Starter」の入手が可能なLattice社のウェブサイトを紹介したチラシが入っているだけだ。そのため、同社のウェブサイトから適切なソフトウエアのファイルをダウンロードする必要がある。最低限必要なのは、基本CPLDモジュール「Primary Module」、「FPGA Module」、合成エンジン「Precision」と同じく合成エンジンのSynplifyである。これらを入手したらライセンスファイルを申請してインストールを実施し、ソフトウエアを起動する。加えて、パラレルポートのドライバも忘れずにインストールしておく必要がある。

次に、ヘルプとユーザーガイドのファイルもダウンロードしてインストールする。環境を理解するにはこれらを利用するのが一番手っ取り早い方法だ。最近リリースされたispLEVERのバージョン6.1では、数多くのアップデートが提供されており、ヘルプシステムも筆者が試したバージョン5.1から大幅に改善されている。旧バージョンを使用しているなら必ずアップデートすることをお勧めする。

MachXOの内部構造

まずは「MachXO Family Handbook」をダウンロードしてデバイスアーキテクチャを理解しよう。MachXOファミリは、256〜2280個のLUT、2Kバイト〜7.5Kバイトの分散SRAM、最大3個の9Kバイト組み込みメモリーブロック、78〜271個のI/Oを備える製品ラインナップである。評価ボードに搭載されているLCMXO256Cは、このファミリの最小サイズの製品だ。ちなみに、2つの上位製品には、最大で2つのPLLが搭載されている。

Lattice社はMachXOファミリをクロスオーバーデバイスと位置付けている。そのLUT構成によるアーキテクチャにより、CPLDとFPGAをクロスオーバーでサポートする。コンフィギュレーションデータをチップ上のフラッシュメモリーに保持するので、外部メモリー間のビットストリームが解読されることもなく、高いセキュリティレベルを実現可能だ。加えて、内部のフラッシュメモリーから広い帯域のデータパスでコンフィグレーションされるために数msで起動できる。

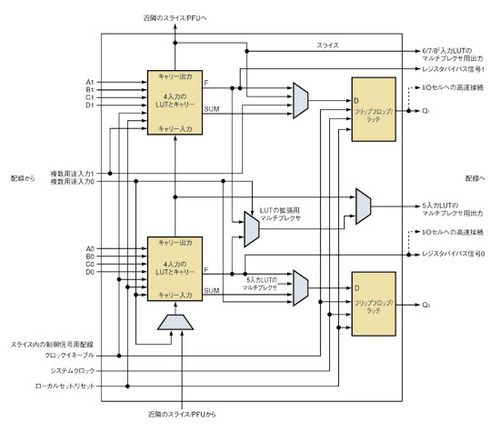

このアーキテクチャではロジックブロックがPFU(プログラマブル機能ユニット)とPFF(ROM/RAMなしのプログラマブル機能ユニット)に分けられている。ロジック、算術演算、レジスタ、分散RAM/ROM機能のブロックはPFUに区分され、PFFはロジック、算術演算、ROM機能に適している。いずれの機能ブロックもそれぞれ4つの「Slice(スライス)」で構成される。各スライスは2つのLUTと出力レジスタを備え、14本の入力信号と7本の出力信号を処理する(図6)。

各スライスは「ロジック」、「リップル(計算用)」、「ROM」、「RAM」の4つの動作モードをサポートしている(ただし、PFFのスライスはRAMモードをサポートしていない)。ロジックモードで複数個の4入力LUTを結合すれば、任意の幅の機能ブロックを合成できる。2ビットのALU(arithmetic and logic unit)を構成可能なリップルモードは、カウンタ機能とコンパレータ機能もサポートしている。RAMモードでは、16×2ビットのメモリーを構成してデュアルポート構成を実現可能である。ROMモードは、書き込みを除いてRAMモードと同じ構成である。ROMへの初期データはコンフィグレーションと同様にプログラミングインターフェースを通じて書き込まれる。配線リソースは2/3/7個のPFU/PFFを縦横に接続する。

クロック分配用の配線には、4つのプライマリグローバルクロック配線と4つのセカンダリグローバルクロック配線がある。これらは12個の内部配線の信号と4つのクロック入力から合成される。

LCMXO256Cは78個のシングルエンドのI/O端子を備えている。そのうち8端子は評価ボードのスイッチに接続され、9端子がLEDに接続される。残りの端子は未使用の端子ヘッダーに接続される。ボードが正常に動作することを確認するためのプログラムが出荷時に書き込まれているが、これも同社のウェブサイトから入手可能だ。

操作性と充実した機能の両立

ispLEVERの最上位にはProject Navigatorが位置付けられ、ここからプロジェクトを開いたり作成したりすることができる。インストールパス内にはexamples\fpga\MachXOディレクトリがある。その下には、VerilogまたはVHDLフォーマットの多数の設計ファイルを格納した6つのディレクトリがある。ここには、16ビットのアップカウンタとダウンカウンタの設計ファイルが納められている。Project Navigatorのヘルプからはウェブブラウザが起動し、使用可能なチュートリアル、ユーザーマニュアル、サンプルプロジェクトの概要が表示される。

MachXO用の「FPGA Schematic and HDL Design Tutorial」には、ispLEVERを用いた、回路図入力と言語入力が混在した設計方法のチュートリアルが含まれている。このチュートリアルは階層構造によってブロック化されており、トップの回路図とブロックシンボルの作成、端子の割り当て、設計ルールのチェック、Verilogモデルの作成などについて学ぶことができる。複数のインスタンスを1つのシンボルに割り当てることが可能であり、階層ナビゲータを使用することでオブジェクトやネットの内容と接続を簡単に確認することができる。

すべてのステップを正しく終えて最後のステージに到達すると、「Design Planner」によってI/O端子の割り当てがチェックされる。筆者が試した際、このチュートリアルではこの時点で2つのエラーが発生し、Design Plannerのスプレッドシートビューを開くことができなかった。しかし、エラーメッセージにはソースファイル内の構文エラーが示され、各メッセージをダブルクリックするとエラー行にカーソルが移動した状態でテキストエディタが開くので、すぐに修正できた。次に「Processes for Current Source」ウィンドウに表示されるフローに沿って、論理設計を実際のチップにフィッティングしていく。このウィンドウでは、設計の現在の状態が追跡される。最後にプログラミング用のファイルを作成し、完成品を物理的にテストする。

優れたソフトウエアツールは、この環境のように直感的に操作できる使いやすさと、パワーユーザーをも満足させる機能を併せ持っているものだ。

開発キット利用時の注意点

本編では、4社の製品について解説してきたが、これらの開発キットに共通して注意しなければならないことがある。それは、パラレルポートがない最近のパソコンでは、パラレルポート経由でFPGAなどにプログラムを書き込むハードウエアを認識できないということだ。

プリンタやドングルのレガシーサポートを組み込んだパラレルEPP/ECP(拡張パラレルポート/拡張機能ポート)カードは、どのメーカーの書き込みソフトウエアでも認識されなかった。Windows XP Proのデバイスマネジャはプリンタポートを認識するが、書き込みソフトウエアが「no kernel driver installed」といったメッセージを表示する。この問題は、プリンタポートとシリアルポートを備えたパソコンに替えたことで解決できた。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

図6 MachXOのスライスの構造 Lattice社製MachXOの各スライスは、2つのLUT機能で構成されている。

図6 MachXOのスライスの構造 Lattice社製MachXOの各スライスは、2つのLUT機能で構成されている。