ESD対策新時代(4/4 ページ)

新たなESD保護設計手法(2)――PCを利用したネットワークESD保護設計

ここまでの説明を通して、サリサイドブロック構造の効果についてもご理解いただけたと思うが、出力トランジスタに同構造を適用できない場合には、どう対応すればよいだろう。あるいは、高耐圧トランジスタ、SOIトランジスタなどを出力トランジスタとして使用する場合にはどうすればよいのだろうか。

従来のESD保護回路は、ESDサージによる電荷を各素子のブレークダウン特性を使用して逃がすことを前提として構成していた。しかし現在では、サリサイド構造トランジスタや高耐圧トランジスタ、SOI/SOS(silicon on sapphire)構造トランジスタなど、ブレークダウンするとすぐに破壊してしまう素子が続々と登場してきている。先述したMixed-Modeシミュレーションによる設計手法などは有効なものには違いないが、さらに発想の転換を行ったESD保護設計の新たな“思想”が必要である。それが、近年、高耐圧デバイスなどの先端デバイス製品で利用され始めた「ネットワークESD保護設計」だ。

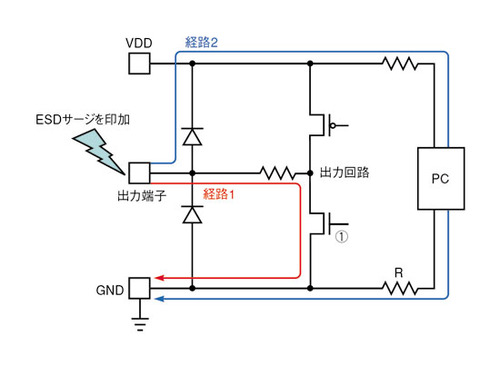

ネットワークESD保護設計とは、簡単にいえば、ブレークダウンすると破壊してしまう素子はブレークダウンさせず、ESDサージの電荷を違う経路で分散させようというものである。図13は、GND端子を基準として出力端子にHBMの正電圧を印加したときの電荷の移動経路である。nチャンネル出力トランジスタ(1)がブレークダウンするとすぐに破壊してしまう構造のトランジスタであるとしたら、経路1には、ESDサージによる電荷が流れないように設計する必要がある。ほとんどの電荷が経路2に流れるようにネットワークESD保護設計を行うのだ。そこでポイントとなるのがPCである。

従来は、ゲート幅の広いGGnMOSをPCとして配置していた。これは、電源‐GND間でのESD印加において、内部回路が破壊しないように電荷の経路として働かせることを目的として行っていた。それ以外の端子へのESD印加では、 すべて、各端子に付加してあるESD保護素子や出力トランジスタなどが電荷の移動経路となり、目標の破壊耐性まで破壊しないように寸法設計がなされていた。それに対し、図13の例であれば、経路2で電荷が移動するようにする。その際には、PCが出力トランジスタ(1)よりも低い電圧で導通し、しかも破壊しないようなものでなければならない。

この種のPC回路の提案は古くから行われていた。分離電源、多電源デバイス構造の進展、ESDに対して脆弱な先端デバイス構造素子といった新たな技術が採用されたことにより、ネットワークESD保護設計が実用的な技術として用いられるようになったのである。

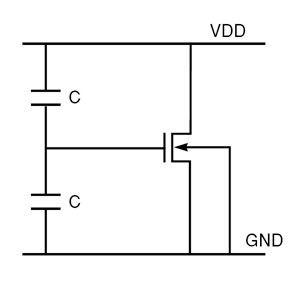

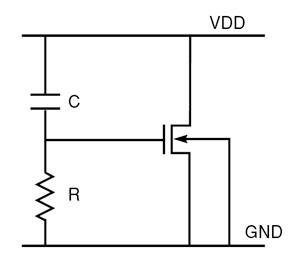

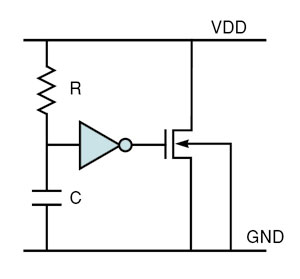

ネットワークESD保護設計には、単純なPCではなく、以下に紹介するような新しいPCが用いられる。図14、15はそれぞれCCタイマーPC、RCタイマーPC*13)と呼ばれるもので、ESDサージ印加時のブレークダウン電圧を低下させて、早くスナップバック動作に入るように工夫されている。図16のGC(gate control)nMOS-PC*14)は、さらにインバータを一段挿入することによって、チャンネル電流動作によって電荷を流してしまうものである。ほかにも、高耐圧デバイスなどではトリガリングSCR-PC*15)が有効な場合もあるが、これについては電源ラッチアップを引き起こすことがあるので注意が必要だ*16)。これらを用いたネットワークESD保護設計を行うために、コンパクトモデルを用いたSPICEシミュレーションによる検証方法も検討されている*17)。

信頼性への影響が新たな課題に

半導体デバイスの開発、LSIの設計において、各種ESD耐性を確保するための保護回路の選択/配置は、従来から定常的な課題であることに違いはなかった。しかし、本稿で説明した通り、ここに来て半導体デバイスの性能向上を実現するためにESD耐性の面で非常に脆弱な先端デバイス構造が次々と採用されてきた。また、ノイズ対策や低消費電力化などのために分離電源方式、多電源方式のLSI設計が採用されるようになり、従来のESD保護回路の考え方では通用しなくなっている。本稿で紹介したMixed-Modeシミュレーションを用いた最適化設計手法やネットワークESD保護設計手法は、従来のようなフェールセーフ的な設計手法とは異なるものだ。すでに、こうした設計手法が求められる新たな時代に突入しているのである。

さらに、次期先端デバイスにおけるESD保護設計の課題として、ESDによる信頼性の劣化を防止する設計の実現が求められる。ESDの印加による半導体デバイスの信頼性的な劣化は従来、無視されてきた事柄だ。しかし、いよいよこの問題が構造的に関係してくることになりそうである。

この課題に対応するには、「ESD試験における製品保証とは」、あるいは「ESD試験における設計保証とは」といった定義の再検討から始める必要がある。また、HBM耐性は実際にはどこまで必要なのか、MM耐性の確保には何の意味があるのかといったことについても検討しなければならない。つまり、機能設計と同様に、「各種ESD耐性に要求される仕様に合致した耐性設計」が求められることになる。そのため、デバイスレベル、モジュールレベル、システムレベルにおける各種ESD要求仕様の合理性が重要となる。

Copyright © ITmedia, Inc. All Rights Reserved.

図13 出力回路における電荷の移動経路

図13 出力回路における電荷の移動経路  図14 CCタイマーPC

図14 CCタイマーPC 図15 RCタイマーPC

図15 RCタイマーPC 図16 GCnMOS-PC

図16 GCnMOS-PC