次世代アナログLSIでは、素子モデルの標準化が急務(2/4 ページ)

MOS FETの次世代標準モデル

表面ポテンシャルモデル(surface potential based model)は、MOS FETの動作をチャンネル内の静電電位の関数として表すことで、物理的な動作を正しく反映し、電流と電圧の特性および導関数を正確に再現する。より正確な導関数を得ることにより、電流の導関数に大きく依存するRFアプリケーションさえも正確にモデル化することが可能になる。

ここまでに説明した通り、最新プロセスに対応した技術や高度なアプリケーションに対しては、従来のVTHベースのモデルでは不十分である(図2)。そこで、CMCは2年前に、次世代MOS FETモデルの標準化に向けて活動を開始した。そのプロセスにおいて、CMCは表面ポテンシャルモデルを標準にすると決めた。そして最近になって、ペンシルバニア州立大学とオランダRoyal Philips Electronics社のPSP(penn state philips)モデルを標準モデルとして選定した*4)。このモデルは広島大学とSTARC(半導体理工学研究センター)が共同開発したHiSIM(Hiroshima University STARC IGFET model)モデルと最終選考で争った。CMCは、当初カリフォルニア大学バークレー校のBSIM5モデルとEKV(Enz-Krummenacher-Vittoz)モデルを候補に挙げていた。選考プロセスでは、90nmのMOSデータを基にした計算効率や堅牢性、CMCがモデルに求める物理的特性などが比較された。その結果、勝ち残ったPSPモデルの標準化作業は現在も行われており、多くのベンダーのシミュレーションプラットフォームがすでにこれを導入している。

脚注:

※4…Gildenblat, Gennady, Hailing Wang, Ten-Lon Chen, Xin Gu, and Xiaowen Cai, "SP: An Advanced Surface-Potential Based Compact MOSFET Model," IEEE Journal of Solid-State Circuits, Volume 39, No. 9, September 2004.

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

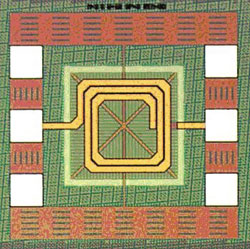

図2 インダクタを用いたRF回路の例 インダクタや抵抗など多くの受動素子に対しては、複雑なモデルが必要となる。現在、そうしたモデルはサブ回路を用いて実現されている。しかし、そのモデルは標準化されていないため、サブ回路の構成時や、シミュレータ間での移行時に誤りが生じる可能性がある(提供:TowerSemiconductor社のSharonLevin氏)。

図2 インダクタを用いたRF回路の例 インダクタや抵抗など多くの受動素子に対しては、複雑なモデルが必要となる。現在、そうしたモデルはサブ回路を用いて実現されている。しかし、そのモデルは標準化されていないため、サブ回路の構成時や、シミュレータ間での移行時に誤りが生じる可能性がある(提供:TowerSemiconductor社のSharonLevin氏)。