【WEB限定記事】シリコンチューナの可能性:1チップで90dBのダイナミックレンジを実現可能(2/3 ページ)

DSP実現のためのプロセス技術

テレビチューナはSNR(信号対雑音比)の制約内で広いダイナミックレンジを達成しなければならない。Xceive社はテレビチューナ用のトランジスタとして、標準的なCMOSよりも優れた特性が得られるシリコンゲルマニウム(SiGe)の技術を採用した。その特徴の1つは、動作電圧が高い点である。動作電圧が高いと、より広範囲の信号を扱うことができ、SNRも大きく向上する。1.0Vの信号に対し10mVのノイズが存在する場合のノイズ比は1%だが、同じ10mVのノイズが3.3Vの信号に入っている場合には、そのSNRは1桁も向上することになる。DSPは信号をクリアにするだけでなく、より高速に信号処理を行うことも可能である。

図2にCMOSおよびSiGeによるトランジスタの遮断周波数と電源電圧の関係を示した。電源電圧3.3Vでは、SiGeを使った場合の遮断周波数はCMOSの場合に比べ4倍も高い。3.3Vで遮断周波数が78GHzのSiGeと同じ性能をCMOSで実現するためには、CMOSの電源電圧を1.2Vにまで下げる必要がある。しかし、それでは信号処理能力に支障が生じてしまう。

2つ目はバイポーラトランジスタの採用により、優れた線形性が実現されていることだ。MOSトランジスタでも線形領域で動作は可能だが、動作電圧が低い場合、その線形領域はバイポーラトランジスタに比べて非常に小さくなってしまう。SiGeのICは、3種類のトランジスタ(シリコンバイポーラ、SiGeバイポーラ、MOS)から成り、高性能で高度な線形回路を実現するのに最適で、しかもノイズ(熱、ショットキ)が最も小さいとされてきた。さらにSiGe BiCMOSプロセスには、同様な製品でよく使われていたGaAs MESFET(metal semiconductor field effect transistor)特有の集積化の制約がない。

SiGeバイポーラトランジスタとCMOSトランジスタを1チップに集積できれば、単一のICチップでアナログ信号とデジタル信号の双方に対応可能なアーキテクチャを構成できる。そうすればテレビチューナなどの用途に最適なチップとなる。ほかの広帯域RFアプリケーションでもSiGeプロセスに注目し始めている。テレビチューナの帯域幅、ノイズ特性、ダイナミックレンジ、隣接チャンネルの干渉除去に関する要件が、この技術に対する要求でもある。

CANチューナをしのぐ性能

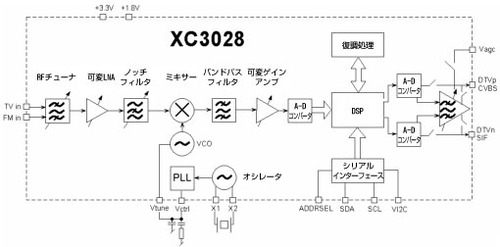

図3にXC3028のブロック図を示す。このブロック図は、同製品がデジタル化と信号処理回路を加えた典型的なスーパーヘテロダインチューナであることを表している。プロセス技術の進歩により、このように完全な機能を、単一のBiCMOSチップに集積することが可能となった。集積された機能には以下のようなものがある。

- 構成可能なフロントエンドフィルタ

- RF、IF、ベースバンドフィルタ

- アナログ復調器

- I2Cインターフェース

- 複数規格に対応する再構成可能なDSP

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

図2 CMOSプロセス(三角形)およびSiGeプロセス(ひし形)の周波数と電圧の関係を表したグラフ

図2 CMOSプロセス(三角形)およびSiGeプロセス(ひし形)の周波数と電圧の関係を表したグラフ 図3 XC3028のブロック図

図3 XC3028のブロック図