D-Aコンバータの アーキテクチャ:Baker's Best

D-Aコンバータの代表的なアーキテクチャであるR2R乗算方式と、R2Rラダー方式について解説する。

今回は、D-Aコンバータのアーキテクチャについて検討してみる。

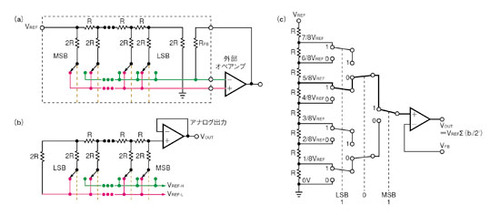

高精度の制御ループに使用される代表的なD-Aコンバータ方式として、R2R型の抵抗を利用した乗算方式(R2R Multiplying DAC)が挙げられる(図1(a))。このタイプの製品としては、分解能が16ビット程度で、INL(integral non linearity:積分非直線性)とDNL(differential non linearity:微分非直線性)が±1LSB以内といった仕様のものが入手できる。この方式では、電流‐電圧変換用に外付けのオペアンプが必要となることが多いが、セトリング時間が比較的短く(例えば0.3μs以下)、広帯域幅(例えば10MHz以上)での変換が可能だという特徴を備える。

産業用途に最も適したものとしては、R2Rラダー方式のD-Aコンバータが挙げられる(図1(b))。この方式では、変換の各タイミングにおいて各2Rがハイまたはローの基準電圧(VREF-HまたはVREF-L)のうちいずれかに接続される。

一般に、R2Rラダー方式のD-Aコンバータの入力は、並列バスである。シリアル入力が可能な製品もあるが、その場合は、内部にシリアル‐パラレル変換用のレジスタを持ち、ラッチされたパラレルデータがD-A変換部への入力となる。入力がパラレル/シリアルいずれの場合にも、抵抗がスイッチングするタイミングのずれ(スキュー)によって出力にグリッチが発生する。R2Rラダー方式は、R2Rを利用した乗算方式と同様にセトリング時間は中程度だが、ノイズが少なく、INL/DNL特性に優れるという特徴がある。

抵抗ストリング方式のD-Aコンバータは、携帯型機器や、閉ループのサーボ制御系、データ捕捉システムなどの用途に適している。図1(c)に示すのは、3ビットの抵抗ストリング方式D-Aコンバータのモデルである。図において、入力はバイナリ値の「101」で、これが(5/8)×VREFの出力電圧に変換される。内部の抵抗ストリング(抵抗列)は、出力段のバッファアンプによって負荷から切り離されているので、負荷変動の影響を受けることがない。

抵抗ストリング方式のD-Aコンバータは消費電力が少なく、入力コードの全域にわたって単調増加性(monotonicity)が確保され、DNL特性に優れている。グリッチも、ほかの方式より少ない。ただし、INL特性については、チップ自体のレイアウトに依存し、抵抗列の均質性に依存する。またノイズは抵抗列のインピーダンスに依存し、その値が比較的大きい。

<筆者紹介>

Bonnie Baker

Bonnie Baker氏は「A Baker's Dozen: Real Analog Solutions for Digital Designers」の著書などがある。Baker氏へのご意見は、次のメールアドレスまで。bonnie@ti.com

Copyright © ITmedia, Inc. All Rights Reserved.