IBISとSPICEのギャップ:Baker's Best

IBIS(I/O buffer information specification)モデルは、プリント基板上の回路の動作をシステムレベルでシミュレーションするためのものだ。主に、外部デバイスから、対象となるデバイスのI/Oバッファへのインターフェースがモデル化される。IBISモデルは、I/Oバッファとプリント基板との間の相互作用は含むが、チップ内部のノード間の相互作用は含まない。

一方、SPICEではチップ内の全トランジスタを対象として動作シミュレーションを行う。SPICEモデルによるトランジスタレベルのシミュレーションでは、出力バッファまでのすべての信号パスが解析の対象となる。しかし、プリント基板のインダクタンス、抵抗、容量の各寄生要素は限られた範囲でしか扱われない。

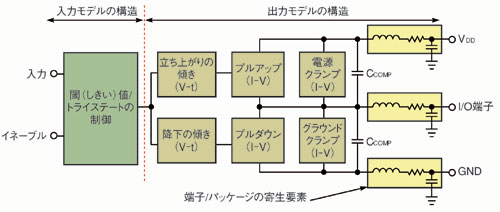

IBISモデルを使えば、システムベースで高速なシミュレーションが行える。IBISモデルでは、ICは外部とどのように相互作用するのかを決めるいくつかの要素によって定義される。信号が高速になると、ICパッケージやプリント基板パターンなどの寄生要素が信号特性に大きく影響する。そのため、すべてのモデルには、端子とパッケージに寄生するインダクタンス、抵抗、容量が定義されている(図1)。

技術者がIBISモデルを使用する理由は何か。それは「速い」からだ。IBISモデルはトランジスタレベルのSPICEモデルと比較して10倍も高速である。従って、IBISモデルを使用すれば、システム設計者は解析時間を節約できる。また、モデルを提供する側のICベンダーにとっても、トランジスタのネットリスト、言い換えれば知的所有権に絡むデータを公開しなくて済むという利点がある。

正確さに関しては、現行のIBIS 3.2/ 4.0モデルはCMOSバッファのインピーダンス特性とスイッチング時間を正確に反映している。これらのバージョンのモデルは電力関連のシミュレーションには適していないが、その点も改善されつつある。

そのほかについては、モデルの正確さはそのモデルがどのようにして作成されたのかによって決まる。対象となるデバイスの評価結果を基にモデルが作成された場合には、そのモデルを用いたシミュレーションでは最大値や最小値といった特性は得られない。一方、SPICEによるシミュレーション結果を基に作成されたのであれば、そのモデルは正確なものとなり得る。ただし、基になったSPICEトランジスタモデルが、蓄積された評価結果に基づいて作成されており、しかもIC設計者によって注意深く見直されたものであることが条件となる。

IBISモデルとSPICEモデルの両方でシミュレーションを行うと、得られる波形に差が見られることがある。そうした相違点の一例として、波形の初期遅延が挙げられる。ここでいう初期遅延とは、シミュレーション波形が出力し始める時間から出力波形が変化し始めるまでの時間のことだ。この現象は、両方のシミュレーションに使用する入力信号と負荷を同じにした場合でも起こり得る。理解困難な症状だが、詳しく調べると、各々の波形に時間的に対応しないところがあることに気付くはずだ。これはなぜか。その理由は、SPICEモデルでは出力バッファに至るまでの全体の遅延がシミュレーション結果に現われるのに対し、IBISモデルによるシミュレーション結果にはこの分の遅延が反映されないからである。

ここで述べた差異については、通常のシミュレーションでは遅延時間が正規化されるため、実際には問題にはならない。しかし、IBISとSPICEの違いを特徴的に示すものである。

<筆者紹介>

Bonnie Baker

Bonnie Baker氏は「A Baker's Dozen: Real Analog Solutions for Digital Designers」の著書などがある。Baker氏へのご意見は、次のメールアドレスまで。bonnie@ti.com

Copyright © ITmedia, Inc. All Rights Reserved.

図1 IBISモデルの構成 IBISモデルには端子とパッケージの寄生要素が含まれる

図1 IBISモデルの構成 IBISモデルには端子とパッケージの寄生要素が含まれる