SiPによるシステムLSIの開発(1/3 ページ)

SiPとSoCには、それぞれにメリット/デメリットがある。筆者らはポータブルオーディオプレーヤ向けシステムLSI製品の開発においてSiPを選択した。本稿では、その開発経過を紹介する。本稿の内容が今後、SiP開発に取り組む方の一助となれば幸いである。

本稿で紹介するのは、筆者ら(austriamicrosystems社)が開発したポータブルオーディオプレーヤ向けシステムLSIの事例である。前書きにも書いたように、われわれは製品化の手法として、SoC(system on chip)ではなく、複数のチップを1つのパッケージに収めるSiP(system in package)を採用した。

われわれの設計チームは、パフォーマンス面でクリティカルな部分のIP(intellectual property)ブロックを自社開発するとともに、外部ベンダーからIPブロックの提供を受けることで、開発期間を短縮し、コストを軽減しようと試みた。しかし、IPの選定/購買基準を慎重に策定したにもかかわらず、複数のIPブロックの統合に際してはいくつかの問題に直面した。

開発作業においてはさまざまなCADツールを活用したが、それでも十分ではなかった。特にハードウエア/ソフトウエアの協調設計とSiP設計の部分は、市販のツールでは十分な効果が得られなかった。製品のパフォーマンスを最大限に高めるには、ハードウエアチームとソフトウエアチームの密接な協力が必要だった。また、開発の初期段階では、DFT(design for testing)とDFM(design for manufacturing)を重要視した。

設計に求められる要件

製品開発は、販売/マーケティング面での要件を考慮し、競合製品の詳細な分析を行うことから始まった。開発する製品はポータブルオーディオプレーヤをターゲットとし、あらゆるオーディオフォーマットに対応する。また、最新のDRM (digital rights management)技術や、バスブースト/イコライザといったオーディオ機能を提供する。高い柔軟性を確保するために、フラッシュメモリーベースのストレージメディアとハードディスクメディアに接続できるようにした。USB 2.0(High Speedモード)のサポートにより、音楽コンテンツをパソコンから高速でダウンロードできるほか、プレーヤ間での高速ファイル交換を可能にするUSB OTG(on the go)機能も組み込んだ。

低価格のポータブルオーディオプレーヤのほとんどは、録音機能の性能が低く、AA/AAAサイズの電池で駆動される。それに対し、高性能のプレーヤはカラー液晶ディスプレイを搭載し、コンパクトディスク相当の音質での録音が可能だ。リチウムイオン電池で駆動され、外部直流電源またはUSBポートに接続できる充電器も付いている。

開発時にこのような分析を行った結果、1つのSoCですべての要件を満たすことはできず、少なくとも2つの製品が必要になることが分かった。1つはすべての機能を備えたハイエンド製品であり、もう1つは機能を絞った低価格製品だ。2つの製品で大きく異なるのは消費電力である。いうまでもなく、その値はプレーヤで音楽を聴く際の再生時間を決める要素になる。

消費電力を最小限に抑えるために、設計チームはオンチップのRAMとプロセッサコアとして「ARM9」を採用することにした。それにより、DC-DCコンバータ、D-Aコンバータ、ヘッドホンアンプを利用するアプリケーションにも十分に対応できると判断した。

また、チップサイズ、組み立てコスト、統合レベルのほか、外部部品の数とコスト、製造工程における出荷テストの時間、歩留りなどについて検討を加え、総コストをできる限り抑えるように努めた。

設計チームはこの時点までに、SoCとSiPの比較を行っていた。両者を比較した場合のSoCの利点は、組み立てコストを抑えられることだ。ウェーハ状態でテストを行い、組み立て作業に移行するまで、1つのチップを処理するだけでよいからである。また、パッケージの構造もシンプルで、内部でクロスカップリングが起きる可能性も小さい。

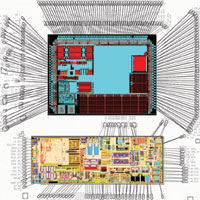

一方、SiPでは、チップ面積のオーバーヘッドとチップ間での信号のやりとりによる電力損失を軽減するために、慎重にチップを分割する必要がある。このような注意点はあるものの、SiPには大きな利点も存在する。デジタル部については、集積度の高い最先端のプロセス技術を用い、アナログ部については電圧の高いプロセスを適用するといったことが行えるのだ(図1)。このプロジェクトでターゲットとしているアプリケーションを考えると、このような分割が行えることのメリットは大きい。確かに、2種類のウェーハ(2つのチップ)を使うため手間はかかるが、ウェーハコスト、ウェーハテスト、組み立て、出荷テストにかかるすべての費用を考慮すると、SiPを使うことでコストは最小限に抑えられるという結論に達した。しかも、SiPを採用することで、プラットフォームといくつかの関連製品を含めた製品ファミリ全体をより短期間で開発できる。

設計チームは2003年末にこのプロジェクトをスタートさせた。そして、デジタルチップには130nmのCMOSプロセスを採用することに決めた。その理由としては、製品に対する要件や、製品の位置付け、IPブロック(特に、プロセッサコアと高集積度のオンチップRAM)の入手の容易さ、2005年初めに予定されていた生産開始時点でのプロセス技術の確度/信頼度などが挙げられる。なお、プロセス技術の確度/信頼度については、プロジェクト開始時点に行ったリスク評価に基づいて推測した。

主にオーディオ機能と電力管理機能から成るオーディオチップは、電源電圧が3.3V/5Vで、PIP(polysilicon insulator polysilicon)コンデンサを利用した0.35μmのCMOSプロセスによって実現した。当社は、このプロセスで実績のある、高度に最適化された IPブロックを数多く有している。そのため、ハイエンド製品用/低価格製品用のチップを開発するに当たり、パフォーマンスをより強化し、面積を最小化するよう精査することができた。

マーケッタ、製品マネジャ、デジタル/アナログのハードウエア設計者、ソフトウエア設計者から成るチームにより、システム定義を策定した。彼らは前世代製品からの知識を生かして数多くの改良を行った。事例分析の結果に従い、米Mentor Graphics社製「Seamless」などのツールと、数々のFPGAプロトタイプを使ってアーキテクチャを最適化した。EDAツールの機能だけでは不十分であったため、設計者らはスプレッドシートを使って数多くの計算を行った。

脚注:

※1…Hsiu, L, M Goldman, R Carlsten, A Witulski, and W Kerwin, “Characterization and Comparison of Noise Generation for Quasi-Resonant and Pulsewidth-Modulated Converters,” IEEE Transactions on Power Electronics, Volume 9, No. 4, July 1994.

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

図1 SiP製品のチップ構成

図1 SiP製品のチップ構成