マルチコア時代の牽引役は最新メモリーアクセス技術:Microprocessor Forum 2007特別リポート(1/3 ページ)

2007年5月21日〜23日、米国サンノゼにおいて「Microprocessor Forum 2007」が開催された。フォーラム全体を通じて見えてきたのは、マルチコアプロセッサの普及が進む中、そのメリットを追求するために、各企業がメモリーアクセス技術にポイントを置いて開発を行っていることだ。

マルチコアが抱える課題

マイクロプロセッサの世界で、マルチコアが大きな潮流となった理由は何か。1つは、動作周波数を上げることだけで処理性能を高めることができなくなったことである。プロセッサの動作周波数を上げると、それに比例して消費電流が増加する。加えて、高速動作のためには、ある程度高い電源電圧を確保する必要がある。そのため、消費電力が大幅に増えてしまう。消費電力が増加すると、パソコンなどの機器では放熱が問題となる。携帯電話端末のように電池を使用する機器では、消費電力の多寡が製品の稼働時間、ひいては製品の商品価値を決める重要な要素になる。もう1つの理由は、半導体製造プロセスの微細化が進み、それによって1つのチップ上に膨大な数のトランジスタを集積できるようになったことだ。このことが、複数のプロセッサコアを1つのチップに組み込むことを可能にした。

消費電力の問題と微細化の進展という2つの背景から、クロック周波数を抑えて消費電力を削減しつつ、プロセッコアサの数を増やすことでパフォーマンスを向上させる手法がトレンドとなった。これが、マルチコアプロセッサが主流となった理由である。

しかし、マルチコアプロセッサのメリットは、単に複数のコアを集積すれば得られるというわけではない。処理の効率化を図るためには、演算能力に見合った高いメモリー帯域(データの転送レート)と遅延の少ないアクセス速度を実現する必要がある。Microprocessor Forum 2007では、このテーマが焦点となった。

メモリーアクセスが効率化の要

米Intel社は、テラフロップス(テラFLOPS:1秒間に1兆回の浮動小数点数演算)規模の演算能力を備える「Tera-scale Research Processor(TRP)」についての講演を行った。その中心にあったのは、マルチコアプロセッサにおけるキャッシュメモリーの在り方だ。

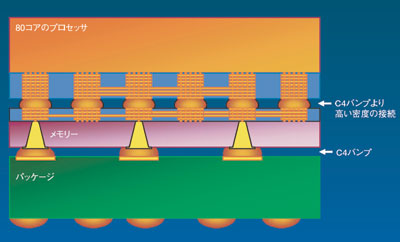

TRPは、80個のコアを1パッケージに集積したプロセッサである。タイルと呼ばれる個々のコアは、2Kバイトのデータメモリーと3Kバイトの命令メモリー、2個の浮動小数点演算ユニット、内部接続用のクロスバールーターを備える。このように、個々のコアは、少ないメモリー容量しか備えていないが、それぞれのコアから個別にアクセス可能なSRAMメモリーを別チップとして積層することによってキャッシュメモリーの容量を確保する。このキャッシュメモリーとプロセッサの接続は、図1のようなオンダイコネクトとする。それにより、高いメモリー帯域と小さいアクセス遅延を実現する。

もちろん、図1の工夫以外にも、メモリーアクセスに関する多くの新技術の開発が行われている。TRPのように、80個にも及ぶ多数のコアが動作する場合には何が必要になるのか。同社は、以下の4つの技術を提案した。

■階層メモリー構造

Intel社は、1つの巨大なメモリーを用いるのではなく、用途に応じて細分化されたメモリー構造を用意する手法を検討している。この階層メモリーは、個々のコアが備える16Kバイト〜64KバイトのL1キャッシュメモリー、関連する処理を行う数個のコア間で共有される256Kバイト〜1Mバイト程度のL2キャッシュメモリー、すべてのコア間で共有される8Mバイト〜32Mバイト程度のL3キャッシュメモリーで構成される。

複数のコアでスレッドを処理する場合、コア間でキャッシュの複製処理を行う必要がある。L2キャッシュメモリーを共有することにより、この複製処理を削減することができる。また、個々のコアにL2キャッシュを備えるよりも面積効率を高められる。

■NCIDの採用

NCID(non-inclusive cash, inclusive directory)は、L2キャッシュメモリーとL3キャッシュメモリーの間に用いる技術である。NCIDを利用する場合、通常であればL3キャッシュメモリーに置くべきL2キャッシュメモリーのデータを保存しない。その代わりに、L2キャッシュメモリーが外部メモリーのどのアドレスから複製されたのかを表すディレクトリ情報をL3キャッシュメモリーに保存する。ほかのコアがキャッシュしているメモリーを読み出したい場合には、そのディレクトリ情報を使ってスヌープフィルタ処理を行うことが可能だ。

NCIDを用いることの利点は、L2キャッシュメモリーの情報が書き換えられてもL3キャッシュメモリーでそれと同じ処理をする必要がないことだ。これにより、無駄にメモリーアクセスが発生するのを避けることができる。

■L4キャッシュメモリーの内蔵

3つ目の工夫は、パッケージ内に配置されたDRAMベースのL4キャッシュメモリーである。3Dスタック、あるいはマルチチップパッケージ(MCP:multi chip package)により、1つのパッケージ内にL4キャッシュメモリーとしてDRAMを配置する。これにより、高いメモリー帯域を実現し、アクセス遅延を回避することができるというメリットが得られる。

■QoSの導入

もう1つの工夫は、キャッシュメモリーへのQoS(quality of service)の導入である。これは、例えば複数の仮想マシンを1つのプロセッサ上で動作させる場合に、優先度の高いアプリケーションに対してより大きなサイズのキャッシュメモリーを動的に割り当てたりするというもの。優先度の低いアプリケーションが大きなキャッシュメモリーを消費することで、優先度の高いアプリケーションの処理が遅れるのを避けることができる。結果として、キャッシュメモリーリソースの有効活用が実現される。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「通信エラー」の原因を追う――搬送機器のコントローラーを修理【前編】

- ARM台頭にルネサス誕生……時代に翻弄され続けた日立「SuperH」

- Ankerがイヤホン用AIチップ、NORフラッシュベースCiM処理

- 「解読不可能」を破る量子コンピュータ――今から始める暗号セキュリティ

- Intelが「Core Series 3」モバイルプロセッサ、エッジ機器向けに

- フェライト(3) ―― 電子部品としてのフェライト

- アルミ電解コンデンサー(1)―― 原理と構造

- AI/HPC用ガラスビア向け 低収縮特性の銅ナノペースト

- SDVとは? 定義や課題、時代に合わせたモビリティDX戦略の重要性

- 次世代車載向けセキュリティコントローラー

図1 TRPとメモリーを積層するスタック構造 TRPでは、キャッシュメモリーとプロセッサチップの接続にスタック構造の採用が考えられている。

図1 TRPとメモリーを積層するスタック構造 TRPでは、キャッシュメモリーとプロセッサチップの接続にスタック構造の採用が考えられている。