ΔΣ型A-DコンバータのS/N比:Baker's Best

時と場合に応じて適切なものを使うのは重要なことである。これは、ΔΣ変調方式を利用したA-Dコンバータ(以下、ΔΣ型A-Dコンバータ)を扱うときにもいえることだ。ΔΣ型A-Dコンバータの基本概念は1930年代に考え出されたものだが、この概念に基づく回路構成には少々特異な面がある。にもかかわらず、ΔΣ型A-Dコンバータをシンプルな方式のA-Dコンバータと同じ基準で判断/対処しようとする例が多く見受けられる。

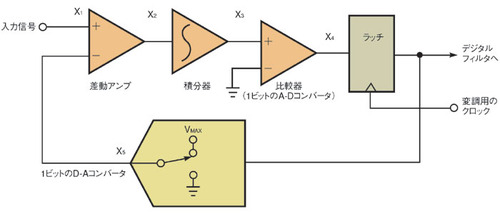

ΔΣ型A-Dコンバータは、単純な仕組みでアナログ‐デジタルの変換を行うわけではない。このタイプのA-Dコンバータは、オーバーサンプリング回路、変調器、デジタルフィルタで構成される。まずオーバーサンプリングによって量子化ノイズを広い周波数範囲に拡散しつつ、周波数成分に変調をかけることで低周波域のノイズを高周波域に追いやる。その上で、デジタルフィルタによって帯域制限処理や間引き処理を行って本来のサンプリングレートに戻すという仕組みだ。

逐次比較型など、通常のNビットA-Dコンバータの理論S/N比(信号対雑音比)は、6.02N+1.76dBで表される*1)。一方、ΔΣ型A-DコンバータのS/N比は6.02(N+NINC)+1.76dBと表せる。ただし、この式におけるNはΔΣ型A-Dコンバータ内部の変調器のビット数であり、A-Dコンバータ全体としての分解能を表すビット数ではない。また、NINCは系全体による分解能の改善分に相当するビット数であり、次式によって求められる。

この式において、Mは変調器の次数であり、Kはオーバーサンプリング比率である。理想的な条件では、1次/Nビットの変調器を持つΔΣ型A-DコンバータのS/N比は6.02N+1.76−5.17+30log10Kとなる(図1)。この理論式は、変調器を構成するA-DコンバータとD-Aコンバータ(多くの場合、分解能は1ビット)が、リニアリティ、ノイズ、オフセット誤差などの面で理想的な性能を備え、デジタルフィルタが理想的なブリックウォール応答を実現する場合にのみ成立する。もちろん、このような理想的な特性は現実の回路では期待できない。

現実のΔΣ型A-Dコンバータを扱う際には、特性にかかわるこのような理論を理解した上で、実測データを基にさまざまな判断を行う必要がある。実測データの取得時には、入力信号を多数サンプリングし、得られた変換出力からノイズをRMS値として求める。その結果を基に、20log10(VRMS-FS/VRMS-NOISE)という式を用いてS/N比を計算することになるだろう。

<筆者紹介>

Bonnie Baker

Bonnie Baker氏は「A Baker's Dozen: Real Analog Solutions for Digital Designers」の著書などがある。Baker氏へのご意見は、次のメールアドレスまで。bonnie@ti.com

脚注

※1…『A-D性能の理論と現実』(Bonnie Baker、EDN Japan 2007年9月号 p.40)

※2…Baker, RJ, CMOS Mixed-Signal Circuit Design, Wiley-IEEE Press, 2002.

※3…Norsworthy, Steven R, Richard Schreier, and Gabor C Temes, Delta-Sigma Converters: Theory, Design, and Simulation, Wiley-IEEE Press, 1996.

Copyright © ITmedia, Inc. All Rights Reserved.

図1 1次のΔΣ型変調器

図1 1次のΔΣ型変調器