FPGA佀ASIC傪惉岟偵摫偔8偮偺億僀儞僩乮3/3 儁乕僕乯

億僀儞僩7丂儊儌儕乕偺弶婜忬懺偺惂屼

丂FPGA偺傾乕僉僥僋僠儍偵偍偄偰摿桳側張棟偵丄儊儌儕乕偺弶婜壔偑偁傞丅偙偙偱峴傢傟傞偺偼丄傾儖僑儕僘儉偺幚峴傗僗僥乕僩儅僔儞側偳偺弶婜壔偲偄偭偨娙扨側婲摦張棟偱偁傞丅僼傿儖僞偺學悢側偳偺掕悢傪儘乕僪偡傞梕堈側庤抜偱傕偁傞丅

丂ASIC傊偺堏峴偱栤戣偲側傞偼丄ASIC偺儊儌儕乕偺忬懺偑婲摦帪偵晄掕偵側偭偰偟傑偆応崌偩丅偙偺栤戣偵懳偟偰偼偝傑偞傑側懳張朄偑懚嵼偡傞丅桳岠側曽朄偺1偮偼丄ASIC傊偺堏峴帪偵弶婜壔壜擻側儊儌儕乕傪嵦梡偡傞偙偲偱偁傞丅儊儌儕乕偺弶婜壔傪峴偆偨傔偺愱梡僜僼僩儘僕僢僋傑偨偼儔僢僷乕儘僕僢僋傪捛壛偡傞曽朄傕偁傞丅

丂傕偆1偮偺丄偦偟偰嵟傕梕堈側曽朄偼丄儊儌儕乕偑弶婜壔偝傟偰偄傞偐偳偆偐偵埶懚偟側偄傛偆偵僔僗僥儉傪愝寁偡傞偙偲偱偁傞丅FPGA摿桳偺婡擻偵埶懚偟側偄傛偆愝寁偡傟偽丄夞楬偺壜斃惈偑傛傝崅傑傝丄ASIC傊偺堏峴帪偵傛傝懡偔偺僆僾僔儑儞傪揔梡壜擻偲側傞丅偝傜偵偼堏峴偵偐偐傞帪娫傕抁弅偱偒傞丅

億僀儞僩8丂摨婜愝寁偺椼峴

丂ASIC偲FPGA偺儘僕僢僋僎乕僩偱摨偠惈擻偑摼傜傟側偔側傞尨場偺1偮偵抶墑偺栤戣偑偁傞丅偨偲偊傾乕僉僥僋僠儍傗惢憿僾儘僙僗偑摨偠偱偁偭偰傕丄抶墑傪堦抳偝偣傞偺偼擄偟偄丅傑偟偰傗丄65nm僾儘僙僗偺FPGA偐傜130nm僾儘僙僗偺ASIC傊偺堏峴偱偁傟偽擄堈搙偼傛傝崅傑傞丅偦偙偱廳梫偲側傞偺偼摨婜愝寁傪揔梡偡傞偙偲偱偁傞丅

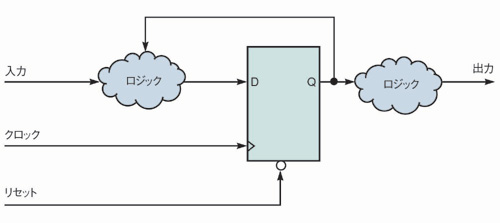

丂摨婜夞楬偺嵟傕婎杮揑側峫偊曽偼丄偡傋偰偺僼儕僢僾僼儘僢僾偵嫟捠偺僋儘僢僋怣崋慄傪1偮梡堄偟丄偡傋偰偺僼儕僢僾僼儘僢僾偵嫟捠偺儕僙僢僩乮傑偨偼僙僢僩乯怣崋慄傪1偮梡堄偡傞偲偄偆傕偺偱偁傞乮恾2乯丅偟偐偟幚嵺偺愝寁偵偍偄偰偼丄暋悢偺僋儘僢僋傪埖傢側偗傟偽側傜側偄偙偲偑懡偄丅偦偺応崌偵偼丄暋悢偺僋儘僢僋怣崋偑屳偄偵懳偟偰擟堄偺帪娫偵曄壔偡傞壜擻惈偑偁傞偲壖掕偟丄巊梡偡傞僾儘僙僗媄弍偵埶懚偟側偄曽朄傪擖擮偵専摙偡傞昁梫偑偁傞丅寢壥偲偟偰丄偝傑偞傑側僴儞僪僔僃僀僋僾儘僩僐儖傗撈棫偟偨僋儘僢僋偱摦嶌偡傞FIFO僶僢僼傽傪帩偮儊僞僗僥乕僽儖側僼儕僢僾僼儘僢僾傪棙梡偟側偗傟偽側傜側偔側傞偐傕偟傟側偄丅偙偆偟偨曽朄偼丄堎側傞幚憰偵堏峴偡傞嵺偺抶墑偺栤戣偼僔儈儏儗乕僔儑儞帪傗FPGA偵傛傞僾儘僩僞僀僾奐敪帪偵偼攃埇偟偒傟側偄偙偲偑偁傞偨傔丄旕忢偵廳梫偱偁傞丅

丂摉慠偺偙偲偩偑丄僠僢僾撪晹偱僋儘僢僋傪惗惉/暘婒偟偨傝丄儕僙僢僩怣崋傪惗惉偟偨傝偡傞偺偼嬌椡旔偗傞傋偒偱偁傞丅偦偺傛偆側怣崋偼丄屳偄偵埶懚娭學傗抶墑傪帩偮偙偲偵側傞偺偱丄幚憰偵傛偭偰堘偄偑惗偠傞壜擻惈偑偁傞丅栤戣偑婲偙傝偑偪側偺偼丄揹椡傪嶍尭偡傞偨傔偵僎乕僥傿僪僋儘僢僋庤朄傪揔梡偡傞働乕僗偱偁傞丅FPGA偵偍偄偰丄偦偺崅偄徚旓揹椡傪嶍尭偡傞偨傔偵偙偺曽朄傪梡偄傞偙偲偑偁傞偐傕偟傟側偄丅偟偐偟丄ASIC偺慡懱揑側徚旓揹椡偼婎杮揑偵FPGA偺偦傟傛傝偐側傝彮側偄丅廬偭偰丄ASIC偱偼僎乕僥傿僪僋儘僢僋庤朄偼晄梫偱偁傞偐傕偟傟側偄丅偙偺庤朄傪揔梡偡傞昁梫偑偁傞応崌偵偼丄昁偢丄側偤昁梫側偺偐丄偡傋偰偺応崌偵偍偄偰惓偟偔摦嶌偡傞偙偲傪偳偺傛偆偵専徹偡傟偽傛偄偺偐偲偄偆偙偲傪僪僉儏儊儞僩偲偟偰巆偟偰偍偔偲傛偄丅偦傟傪婎偵丄堏峴傪扴摉偡傞僠乕儉偲儗價儏乕傪幚巤偡傞偲傛偄偩傠偆丅

丂傎偐偵傕丄桳尷僗僥乕僩儅僔儞偺愝寁偵偍偄偰揔愗側僨僢僪僗僥乕僩張棟傪壛偊傞偙偲丄儔僢僠傪旔偗傞偙偲丄抶墑偵懳偡傞埶懚惈傪彍偔偙偲偲偄偭偨桳岠側庤朄偑偁傞丅偙傟傜偺庤朄傪嵦梡偟丄偱偒傞偩偗惢憿僾儘僙僗偵埶懚偟側偄愝寁傪栚昗偲偡傞偲傛偄丅

丂FPGA偱偼丄儖僢僋傾僢僾僥乕僽儖傪幚憰偡傞偙偲偵傛傝崅懍側暋崌儘僕僢僋婡擻傪幚尰偱偒傞丅偟偐偟丄僾儘僌儔儅僽儖偵愙懕偝傟傞攝慄晹暘偺抶墑偑堦場偱丄ASIC偲偼堎側傞摦嶌偵側傞壜擻惈偑偁傞丅椺偊偽丄彫偝側僌儕僢僠偑惗惉偝傟傞傛偆側慻傒崌傢偣儘僕僢僋夞楬偑偁偭偨偲偡傞丅FPGA偱偼攝慄晹暘偑儘乕僷僗僼傿儖僞偲偟偰婡擻偟丄僌儕僢僠偑尭悐偡傞壜擻惈偑偁傞偑丄ASIC偱偼偦傟偑師偺僎乕僩傊偲揱憲偝傟偰偟傑偆偐傕偟傟側偄丅壖偵偦偺怣崋偑僼儕僢僾僼儘僢僾偺僋儘僢僋抂巕傪嬱摦偟偰偟傑偭偨傝偡傞偲丄栤戣偑惗偠傞壜擻惈偑偁傞丅偙偺偙偲偐傜傕丄摨婜愝寁傪梡偄傞偙偲偑椙偄寢壥偵偮側偑傞偙偲偑傢偐傞丅僋儘僢僋傗儕僙僢僩怣崋忋偵慻傒崌傢偣儘僕僢僋偑懚嵼偟側偗傟偽丄偦偺傛偆側栤戣偑惗偠傞偙偲偼側偄丅

丂摨婜愝寁傪峴偆偲丄堏峴屻偺ASIC偺僥僗僩偑偐側傝梕堈偵側傞丅嵟嬤偱偼丄帺摦揑/敿帺摦揑偵僥僗僩梡儘僕僢僋偺憓擖偲専嵏僾儘僌儔儉偺傾儖僑儕僘儉惗惉傪峴偆DFT乮design for testing乯庤朄偑棙梡偝傟偰偄傞丅傛傝椙偄曽朄偱愝寁偝傟偨夞楬偱偁傟偽丄DFT僣乕儖傕嵟戝尷偵妶梡偱偒傞丅偦傟偵懳偟丄旕摨婜僋儘僢僋傗丄暋悢偺僋儘僢僋丄儔僢僠丄抶墑傊偺埶懚惈傪帩偮夞楬偱偼丄堦斒揑偵僥僗僩僇僶儗僢僕偑掅壓偡傞丅

帠慜偺専摙偑廳梫

丂偙偙傑偱偵徯夘偟偨娙扨側億僀儞僩偵棷堄偡傞偩偗偱丄FPGA偐傜ASIC傊偺堏峴傪傛傝僗儉乕僘偵峴偊傞傛偆偵側傞丅ASIC傊偺堏峴傪峫偊傞側傜丄FPGA偺愝寁傪奐巒偡傞慜偵ASIC儀儞僟乕偵憡択偟偰傒傞偲傛偄丅ASIC儀儞僟乕偼丄僔乕儉儗僗側堏峴傪幚尰偡傞偨傔偺忣曬傗巜恓傪採嫙偟偰偔傟傞偼偢偱偁傞丅摿偵丄ASIC偺奐敪宱尡偑側偄側傜丄ASIC儀儞僟乕偵昁偢憡択偡傞偙偲傪悇彠偟偨偄丅儘僕僢僋僎乕僩偼偳傟傕摨偠傛偆偵偱偒偰偄傞偲巚偭偰偄傞偐傕偟傟側偄偑丄FPGA偲ASIC偼尩枾側堄枴偱摍壙側傢偗偱偼側偄丅FPGA偺愝寁傪奐巒偡傞慜偵丄ASIC儀儞僟乕傪慖掕偟偰曽恓傪嶌偭偰偍偔偲傛偄偩傠偆丅

丂揔愗側ASIC僾儔僢僩僼僅乕儉傪僞乕僎僢僩偲偟丄揔愗側僷僢働乕僕偺慖戰傗抂巕掕媊側偳丄堏峴偵偐偐傢傞寁夋偑偟偭偐傝偲楙傜傟偰偄傟偽丄僐僗僩傪嵟戝尷偵嶍尭偡傞偙偲偑偱偒傞丅IP儔僀僙儞僗偺栤戣傪慜傕偭偰攃埇偟丄FPGA儀儞僟乕偺愱桳IP偱幚尰偟偨婡擻傪偳偺傛偆偵曄姺偡傞偺偐丄傑偨偼曄姺偟側偄傎偆偑傛偄偺偐偲偄偭偨偙偲傪寛傔偰偍偔偙偲偵傛傝丄堏峴帪偺栤戣傪尭傜偡偙偲偑偱偒傞丅慡懱揑側昳幙傪崅傔傞偨傔偵丄偳偺傛偆側愝寁曽朄傪嵦梡偟丄偳偺傛偆側曽朄偼旔偗傞傋偒側偺偐偲偄偭偨偙偲傕峫嶡偟偰偍偔偲傛偄丅

Copyright © ITmedia, Inc. All Rights Reserved.

婰帠儔儞僉儞僌

恾2丂摨婜夞楬偺婎杮峔惉丂偡傋偰偺僼儕僢僾僼儘僢僾偵嫟捠偺1偮偺僋儘僢僋怣崋慄偲丄偡傋偰偺僼儕僢僾僼儘僢僾偵嫟捠偺1偮偺儕僙僢僩乮傑偨偼僙僢僩乯怣崋慄傪梡堄偡傞丅

恾2丂摨婜夞楬偺婎杮峔惉丂偡傋偰偺僼儕僢僾僼儘僢僾偵嫟捠偺1偮偺僋儘僢僋怣崋慄偲丄偡傋偰偺僼儕僢僾僼儘僢僾偵嫟捠偺1偮偺儕僙僢僩乮傑偨偼僙僢僩乯怣崋慄傪梡堄偡傞丅