FPGA佀ASIC傪惉岟偵摫偔8偮偺億僀儞僩乮2/3 儁乕僕乯

億僀儞僩4丂IP偺嵦梡偼怲廳偵

丂ASIC傊偺堏峴傪梕堈偵偡傞偨傔偵丄FPGA傪愝寁偡傞嵺偵偱偒傞偙偲偑偄偔偮偐偁傞丅嵟弶偵峫偊傞傋偒偙偲偼丄IP乮intellectual property乯偺慖戰偱偁傞丅IP偵偼丄愊榓儐僯僢僩丄儊儌儕乕丄FIFO乮first in first out乯僕僃僱儗乕僞側偳偺僔儞僾儖側僽儘僢僋傕偁傟偽丄僾儘僙僢僒丄崅懍僔儕傾儖I/O丄SERDES乮serializer/deserializer乯側偳偺傛傝暋嶨側僽儘僢僋傕偁傞丅捠忢丄偙傟傜偺僽儘僢僋偵偼IP儔僀僙儞僗偺栤戣偑偁傝丄偦偺懡偔偼FPGA儀儞僟乕偺愱桳媄弍偲側偭偰偄傞丅

丂堦尒丄FPGA偺朙晉側柍彏IP偺儕僗僩偼枺椡揑側傕偺偩丅偟偐偟丄幚嵺偵偼戝検偵惗嶻偝傟傞僔僗僥儉傪懳徾偲偟偰偄傞応崌丄FPGA帺懱偑崅壙偱偁傞偨傔偵丄柍彏IP偺儊儕僢僩偑堄枴傪側偝側偄壜擻惈偑偁傞丅ASIC傊偺堏峴傪峴偆偺偱偁傟偽丄偝傜偵栤戣偼暋嶨偵側傞丅

丂偙偺傛偆側棟桼偐傜丄FPGA儀儞僟乕愱桳偺IP偵敍傜傟側偄傛偆偵偡傞愴棯偑昁梫偱偁傞丅愝寁傪奐巒偡傞慜偵丄ASIC傊偺堏峴帪偺IP偺庢傝埖偄偵娭偡傞曽恓傪嶌偭偰偍偔偲傛偄丅椺偊偽丄FPGA撪偱僱僀僥傿僽側僽儘僢僋偵懚嵼偡傞儊儌儕乕傪巊梡偡傞偺偼傛偄偑丄傛傝崅搙側FIFO僕僃僱儗乕僞傪巊梡偡傞偲丄偦傟偑FPGA儀儞僟乕偺愱桳IP偱偁傞壜擻惈偑偁傞丅榑棟崌惉僣乕儖偺儀儞僟乕偑採嫙偡傞FIFO儌僕儏乕儖傪巊梡偡傞偐丄ASIC儀儞僟乕宱桼偱FPGA偺IP傪巊梡偡傞嫋壜傪摼傞傎偆偑偢偭偲梕堈偐傕偟傟側偄丅

丂堦斒揑偵偼丄偱偒傟偽榑棟崌惉偑壜擻側IP傪棙梡偡傋偒偱偁傞丅愝寁慜偵IP偺儔僀僙儞僗傪庢摼偟丄FPGA偲ASIC偺椉曽偱棙梡偱偒傞傛偆偵偟偰偍偔偲傛偄丅ASIC儀儞僟乕偲偲傕偵丄IP偵娭偡傞曽恓傪嶔掕偟偰偍偔偲傛偄偩傠偆丅傑偨丄ASIC儀儞僟乕偼丄擣掕IP儀儞僟乕傗ASIC僨僓僀儞僴僂僗偑曐桳偡傞IP偵偮偄偰壗傜偐偺採埬傪偟偰偔傟傞偐傕偟傟側偄丅FPGA儀儞僟乕偑採嫙偡傞IP傪棙梡偡傞偲寛掕偟偰偟傑偄丄ASIC梡偵偼捛壛偺儔僀僙儞僗椏傪巟暐傢側偔偰偼側傜側偄忬嫷偵娮傞慜偵丄儔僀僙儞僗偵娭偡傞岎徛傪峴偆偙偲偑廳梫偱偁傞丅

億僀儞僩5丂僞僀儈儞僌惂栺傪攃埇偡傞

丂僞僀儈儞僌惂栺側偳偺婎杮揑側巇條傕峫椂偡傋偒億僀儞僩偱偁傞丅椺偊偽丄FPGA偵偍偗傞NAND僎乕僩偼偳偺偔傜偄偺懍搙偱摦嶌偟丄ASIC偺NAND僎乕僩偼偳偺偔傜偄偺懍搙偱摦嶌偡傞偺偩傠偆偐丅廳梫側偺偼丄僔僗僥儉偱昁梫偲側傞偺偼丄偳傟偔傜偄偺懍搙偱摦嶌偡傞NAND僎乕僩側偺偐偲偄偆偙偲偩丅僔僗僥儉撪偱摦嶌偡傞僠僢僾偺僞僀儈儞僌巇條偼廳梫偱偁傝丄僔僗僥儉慡懱偺僞僀儈儞僌惂栺傪棟夝偡傞偺偼偝傜偵廳梫側偙偲偱偁傞丅

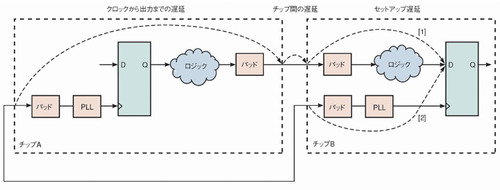

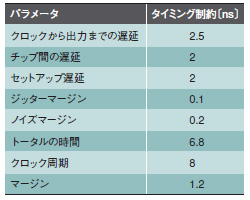

丂恾1偼僞僀儈儞僌惂栺傪枮偨偟側偑傜摦嶌偡傞2偮偺僠僢僾偺奣梫傪昞偟偰偄傞丅僞僀儈儞僌偵娭偡傞奺庬僷儔儊乕僞偺嬶懱揑側抣偼昞1偺傛偆側傕偺偲側傞丅

丂儅乕僕儞傕娷傔偰丄僞僀儈儞僌惂栺偵娭偡傞偡傋偰偺僷儔儊乕僞傪棟夝偟偰偍偔偙偲偼丄堏峴嶌嬈偵栶棫偮丅ASIC偵偍偄偰傛傝掅僐僗僩壔偑恾傟傞媄弍傪棙梡偱偒傞偺側傜偽丄堏峴傪扴摉偡傞媄弍幰偼丄慡懱揑側惂栺傪枮偨偟偮偮丄偝傑偞傑側僞僀儈儞僌僷儔儊乕僞傪挷惍偡傞偙偲偵側傞偩傠偆丅媡偵僞僀儈儞僌惂栺傪棟夝偟偰偄側偗傟偽丄FPGA偺僞僀儈儞僌僷儔儊乕僞偺斖埻傪挻偊偰偟傑偄丄晄梫側僐僗僩偑偐偐傞壜擻惈偑偁傞丅愝寁偵梡偄偨媄朄傗丄摿暿側僞僀儈儞僌梫審丄婲摦帪偺梫審丄揹尮掆巭儌乕僪側偳丄愝寁偵娭偡傞摿婰帠崁偼偡傋偰楍嫇偟偰偍偔偙偲偑廳梫偱偁傞丅堏峴屻偺僠僢僾偑堄恾偳偍傝偵摦嶌偡傞偙偲傪曐徹偡傞偨傔偵偼丄偙傟傜偺忣曬偑昁梫偲側傞丅

丂堏峴嶌嬈偼丄偍偦傜偔RTL僐乕僪偐傜奐巒偡傞偙偲偵側傞偩傠偆丅偦偺嵺偵偼丄僐乕僪偑惍棟偝傟偰偄偰僪僉儏儊儞僩壔偝傟偰偄傞偲搒崌偑椙偄丅FPGA偺愝寁幰偼丄崌惉梡僗僋儕僾僩偲僞僀儈儞僌惂栺僼傽僀儖傪採嫙偡傞昁梫偑偁傞丅夞楬偺堦晹傑偨偼慡懱傪僱僢僩儕僗僩宍幃偱採嫙偟側偗傟偽側傜側偄働乕僗傕偁傞丅偦偺応崌偵傕丄峔惉傪帵偡僪僉儏儊儞僩傗丄崌惉梡僗僋儕僾僩丄僞僀儈儞僌惂栺僼傽僀儖偑懚嵼偡傞偙偲偑朷傑偟偄丅夞楬偵傛偭偰偼丄堏峴偺惉斲傪専徹偟偨傝丄揹椡僔儈儏儗乕僔儑儞傪幚峴偟偨傝偡傞偨傔偺僥僗僩儀儞僠傪採嫙偡傋偒偩傠偆丅

丂桳梡側僥僗僩儀儞僠傪嶌惉偡傞偨傔偵偼丄擖椡偺僉儍僾僠儍偲墳摎偺梊應偑峴偊傞偐斲偐偑僇僊偲側傞丅偙偺忣曬傪採嫙偡傞嵟椙偺曽朄偼丄抂巕偺忬懺曄壔傪婰弎偡傞VCD乮value change dump乯僼傽僀儖傪巊梡偡傞偙偲偱偁傞丅惓妋側僞僀儈儞僌偱偺忣曬偑昁梫偲側傞偺偱丄僉儍僾僠儍僔儈儏儗乕僔儑儞偼嫋梕抶墑儌乕僪乮assignable delay mode乯丄傑偨偼僼儖僞僀儈儞僌惛搙偱幚峴偡傞偙偲偑昁恵偩丅僛儘抶墑儌乕僪傗儐僯僢僩抶墑儌乕僪偱偼丄抂巕偺僨乕僞僼傽僀儖偵惓妋側抣傪斀塮偝偣傞偙偲偑偱偒側偄丅

億僀儞僩6丂婲摦愝掕偵偮偄偰偺峫嶡

丂婲摦帪偵挿戝側僾儘僌儔儈儞僌偲峔惉僔乕働儞僗偑昁梫側FPGA偲偼堎側傝丄ASIC偼杮幙揑偵偦偺傑傑巊梡壜擻側晹昳偱偁傞丅偟偐偟丄ASIC傊偺堏峴傪慜採偵偡傞側傜丄FPGA偺愝寁傪奐巒偡傞帪揰偱丄婲摦帪偺怳傞晳偄偵偮偄偰傕拲堄傪暐偭偰偍偔昁梫偑偁傞丅FPGA偺僾儘僌儔儈儞僌偵傛偭偰幚尰偝傟傞婡擻傗怣崋偵僔僗僥儉偑埶懚偡傞応崌丄ASIC偵堏峴偟偨嵺偵栤戣偑惗偠側偄傛偆偵偟偰偍偐側偗傟偽側傜側偄丅埶懚偺壜擻惈偑偁傞椺偲偟偰偼丄僾儘僌儔儈儞僌偑惓偟偔峴傢傟偨偙偲傪妋擣偡傞偨傔丄偁傞偄偼僔僗僥儉儕僙僢僩偺夝彍傗暿偺婲摦僔乕働儞僗偺堦晹偱丄乽done乿抂巕傪娔帇偟偰偄傞応崌側偳偑嫇偘傜傟傞丅傎偐偺椺偲偟偰偼丄偄偔偮偐偺FPGA偺偆偪偺偄偢傟偐傪ASIC偵堏峴偡傞偙偲側偔偦偺傑傑巊梡偡傞偙偲傪寁夋偟偰偍傝丄側偍偐偮暋悢偺FPGA傪僨僀僕乕僠僃乕儞偲偟偰埖偭偰峔惉傪幚巤偡傞傛偆側働乕僗偵傕拲堄偑昁梫偱偁傞丅

丂傕偆1偮丄婲摦偵娭偟偰峫椂偟側偗傟偽側傜側偄偺偼丄傾僫儘僌揑偵峴傢傟傞POR乮power on reset乯傪揔愗偵張棟偡傞偙偲偱偁傞丅堎側傞惢憿岺掱偱惢憿偝傟偨FPGA偺POR偑丄傑偭偨偔摨偠傛偆偵摦嶌偡傞偙偲傪婜懸偟偰偼側傜側偄丅摉慠丄ASIC偺POR偲FPGA偺POR傕姰慡偵摨偠摦嶌偲偼側傜側偄丅僔僗僥儉慡懱梡偺POR怣崋傪惗惉偡傞僠僢僾偑僔僗僥儉撪偵1偮偩偗懚嵼偡傞傛偆偵偡傞偺偑椙偄愝寁偱偁傞丅偙傟偵傛傝丄僞僀儉僔乕働儞僗偺栤戣偑惗偠傞壜擻惈偑梷偊傜傟丄僔僗僥儉偺婲摦偺怣棅惈傪崅傔傞偙偲偑偱偒傞丅POR怣崋偺惗惉偵偼丄FPGA/ASIC偺偳偪傜傪巊梡偟偰傕傛偄偑丄偦偺婡擻傪扴偆僠僢僾偼僔僗僥儉撪偵偨偩1偮偵偡傋偒偩偲偄偆偙偲偱偁傞丅

Copyright © ITmedia, Inc. All Rights Reserved.

婰帠儔儞僉儞僌

恾1丂2偮偺僠僢僾偵偐偐傢傞僞僀儈儞僌惂栺

恾1丂2偮偺僠僢僾偵偐偐傢傞僞僀儈儞僌惂栺 昞1丂僷儔儊乕僞偛偲偺僞僀儈儞僌惂栺丂

昞1丂僷儔儊乕僞偛偲偺僞僀儈儞僌惂栺丂