マルチストローブによるソース同期I/Fの試験:タイミングマージンの減少に対処(1/2 ページ)

データ転送を高速に行う最近のICは、外部インターフェースとして、ソースシンクロナス方式を採用している。このインターフェースをICの自動試験装置(ATE)によって正確に試験するには、タイミングマージンの減少に対処しなければならない。本稿では、その対処法としてマルチストローブを用いる手法を紹介する。

ソースシンクロナスI/Fの普及

機器の高性能化に伴い、その部品として用いられるICにもより高い性能が求められるようになった。最近のICは、データ転送を高速に行うための外部インターフェース(以下、I/F)として、ソースシンクロナス(同期)I/Fを採用している。ソースシンクロナスI/Fとは、送信側が同期用のクロック(出力クロック)を供給するタイプのI/Fである(別掲記事『ソースシンクロナスI/Fの概要』を参照)。従来は、受信側と送信側に同じ同期クロックを供給して通信するコモンシンクロナスI/Fが使われていた。しかし、このI/Fでは配線遅延などの問題により高速化が難しくなったことからソースシンクロナスI/Fが考え出された。最近では、多くのICがPCI ExpressやDDR SDRAM(double data rate synchronous dynamic random access memory)、EV6バスなどに代表されるこの方式のI/Fを備えている。

このソースシンクロナスI/Fのセットアップ時間やホールド時間をATE(automated test equipment:自動試験装置)を用いて試験する場合、位相ジッターや位相ドリフト、スキューなどの影響を受けて試験が正確に行えないという問題がある。これは、一般的なATEが、対象とする信号に対して、タイミングが固定された1つのストローブを用いて検査を行っていることに起因する問題である。つまり、測定対象の位相が動的に変化する場合、タイミングマージンが減少して正確な試験が行えないのだ。特に高速なクロックを用いるソースシンクロナスI/Fを試験する際にはこの点に注意する必要がある。

ソースシンクロナスI/Fの概要

高速なクロックを用いるICにおいては、そのクロックをIC内の配線によって分配するだけでも、信号品質や同期の面でさまざまな問題が生じる。その問題に対処するために、リファレンスクロックからPLL(phase locked loop)によって安定な複数のローカルクロックを生成し、小規模に分割された個々のブロックにそれを分配する手法が用いられる。つまり、複数のローカルクロックを、複数の小規模なクロックドメイン(ブロック)に分割されたI/Oインタフェースなどに供給して動作させるのである。

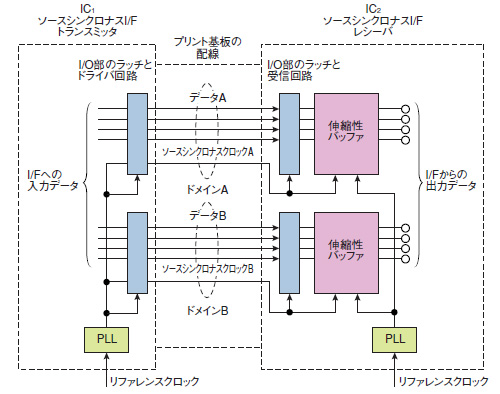

図Aは、2個のICの間で1方向にデータを伝送するソースシンクロナスI/Fの構成例である。一般的にこのようなI/Fでは、I/Oブロックが数個のクロックドメインごとに分割されており、各クロックドメインは4〜8本のデータラインとそれに対応するソースシンクロナスクロック(出力クロック)から構成される。

データとソースシンクロナスクロックは、それらの間のスキューとジッターが最小になるよう同等の特性を備えた別な駆動回路から出力される。受信側では、そのソースシンクロナスクロックを用いてデータをラッチする。このような動作であるため、共通位相ジッターに起因する位相の変動があってもデータの受信に問題は生じない。つまり、ソースシンクロナスI/Fを用いれば、セットアップ時間、ホールド時間のマージンが増大する。結果として、高速I/Fの同期の問題に対するタイミング条件が緩和されることになる。

Copyright © ITmedia, Inc. All Rights Reserved.

図A ソースシンクロナスI/Fの構成例 ソースシンクロナスI/Fでは、リファレンスクロックを基に、IC内部のPLLによって複数のローカルクロックを生成する

図A ソースシンクロナスI/Fの構成例 ソースシンクロナスI/Fでは、リファレンスクロックを基に、IC内部のPLLによって複数のローカルクロックを生成する