40nm時代のIC設計アプローチ:「マスク修正なし」を実現するための方策とは?(1/2 ページ)

プロセスの微細化が進むに連れ、設計者にとって最新プロセスへの移行はより難易度の高いものとなってきている。本稿では、Altera社が40nmプロセスでのFPGA製品開発で実践したアプローチを例にとり、最新プロセスへの移行をスムーズに実現するためのポイントを紹介する。

最新プロセスのリスク

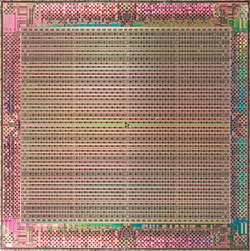

ICの製造プロセスを新世代のものへと移行する際には、常に新たな設計上の課題がつきまとう。中でも40nmプロセスノードへの移行は、過去のプロセスノードへの移行時と比べて、とてつもなく大きな困難とリスクを伴う作業になる。複雑さ、回路規模、設計コストが増大するため、1回の設計工程で確実にチップを動作させるには、新たな体系的手法の導入が不可欠となる(写真1)。その体系的手法では、テストチップと統計的シミュレーションを活用することが必要になる。

40nmプロセスを利用する場合、設計者は多大なリスクに直面することになる。新たな設計課題を解決しなければならないし、設計ミスが発生した場合の代償は従来よりも大きい。マスクの製作コストは、プロセス技術の世代が進化するごとに約50%の割合で増加しており、40nmプロセスのマスクコストは300万米ドルを超えている。設計コストも同じくらいに大きな問題だ。設計コストが増大するペースは、マスクコストのそれよりも急激である。論理ゲート数の増大とチップ設計の複雑化がこの状況を生み出している。

こうした理由から、IC設計者は技術的な課題と経済的な課題の両方に対処可能な手法を導入する必要に迫られている(別掲記事『FPGAとASICの製造プロセス』を参照)。その有力な候補が、設計工程の初期からテストチップを検証に利用する手法である。設計のさまざまな段階で、テストチップを設計ブロックの検証に使うのだ。筆者らが所属するAltera社は、90nm世代のプロセス技術を採用する段階で、この手法を導入した。その後、65nm、40nmのプロセスノードに移行する際にも同じ手法を採用した。その結果、マスク修正を発生させることなく、製品化を実現することができている。

この手法は設計資産の再利用を促し、開発コストの削減ももたらした。さらに、新世代の製造プロセスを開発するするときの課題の解決も容易にした。

「テストチップ」が鍵に

テストチップによる回路設計の検証とプロセスの特性の検証は、膨大な数の設計課題への対応に役立つ。

最初のテストチップは設計工程の初期段階で使用する。基本的な論理ブロックや個別のトランジスタ、配線の接続を検証するためのチップである。テストチップの設計は、プロセスモデルとシミュレーションモデルを完成させる前の段階で始めることができる。そのため、新しい世代のプロセスへの移行をスムーズに進められる。

この段階でのテストチップは、設計ルール群の検証と、修正の必要なルールの抽出に役立つ。最終的な設計による回路を、期待どおりに動かすことにつながる作業である。IC設計チームには、ファウンドリ企業と緊密に連携しながら作業を進めることが求められる*1)。ディープサブミクロンプロセスで発生する問題を理解するためだ。

テストチップは、プロセスノードの変更に伴って、ディープサブミクロンで発生する新たな現象を見つけ出すのにも役立つ。そうした現象は、しばしばプロセスのテスト用に使われた素子/回路/構造よりも、実際の回路において顕著に現れる。従って、テストチップは期待どおりに動作しないはずである。期待する動作と実際の動作の違いの補正を試みることが、設計チームがそれまで把握していなかった現象の同定に役立つ。またテストチップにより、設計者が知ってはいるけれども完全には理解していなかった現象が、回路にどのような影響を与えるかを把握できる。

設計工程の後半になって重要な現象をすべて把握し、設計ルール群がより安定してきたら、次の段階のテストチップを使う。大規模な回路ブロックを評価するためのテストチップである。また、論理回路の新しいレイアウトが新世代のプロセスで製造しても適切に動作するかどうかを確かめたり、既存の論理回路のレイアウトを新世代のプロセス向けにシュリンクしたときに不具合が起きないかどうかを確かめたりする。

テストチップによる評価結果は、ハードウエア/ソフトウエア設計資産の再利用による開発期間の短縮とコストの削減を促進することに役立てることができる。機能に不完全なところがあったり、あるいは回路ブロックの性能改善が必要だったりした場合、設計者は開発プロジェクトの早い段階で必要な対策を施す機会を得ることになる。なお、この段階でのテストチップには精緻な調整を必要とする回路も搭載する。メモリー回路、PLL(Phase Locked Loop)回路、高速I/O回路などである。この段階では、これらの回路のテストが非常に重要な意味を持つのだ。

設計工程がさらに進んだら、複数の回路ブロックを統合したときの評価に用いるテストチップを使用する。また、そのテストチップは設計初期のテスト結果に応じて、設計に修正を施した個所の評価にも使う。

開発プロジェクト全体で何種類のテストチップを使うかによって、設計完了までに修正や改善などを加えられる回数が決まる。Altera社の開発プロジェクトでは、合計で9種類のテストチップを使用した。設計期間に換算すると、3〜4カ月ごとに1種類のテストチップを利用していたことになる(表1)。

テストチップを使った開発手法は、設計完了後に一度の試作で完全に動作するチップが得られる(すなわち、そのまますぐに量産に移行できる)可能性を大きく高める。しかし、テストチップ用のマスクを数多く使用することになるので、開発プロジェクトのコストが大幅に増えてしまうのではないかとの懸念が生じるはずだ。これはもっともなことではあるが、実際には、ファウンドリ企業の台湾TSMC(Taiwan Semiconductor Manufacturing Company)社が提供している「Shuttleプログラム」のようなサービスを利用すれば、テストチップのコストを低減できる。

ファウンドリ企業が新しい世代の製造プロセス技術を開発する際には、膨大な数のテスト用ウェーハを生産ラインに投入する。デバイスの特性評価と製造条件の最適化のためである。さらに、製造プロセスの変動をチェックするためのテスト用ウェーハも定期的に生産ラインに投入する。ファウンドリ企業と緊密な関係にあれば、設計工程の初期に使う簡単なテストチップはファウンドリのウェーハに相乗りできることがある(テストチップのマスクをファウンドリの使用するマスクに含める)。Shuttleプログラムまたは類似のプログラムを利用すれば、より大規模な回路のテストチップまたは全体回路のテストチップをコストを抑えて製造できる。こうしたプログラムを利用した場合のコストは、3mm×4mmのシリコンチップ(ダイ)を40nm技術で製造するケースで、マスクセット全体のコストの5%以下で済む。

テストチップを使った開発プロジェクト全体でのマスクコストは、マスクセット全体のコストを上回る可能性がある。ただし、設計作業を効率化できたという効果を見逃してはならない。設計資産を再利用し、設計上の不具合を早期に発見することのコスト削減効果は、テストチップのコストをはるかに上回るのである。

40nmプロセスで製造するICを開発するには、テストチップを利用した新しい手法を活用するとともに、既存技術を改良したり、設計パラメータを調整したりといった作業が必須となる。特に40nm世代では、次の3つの項目が重要である。

- プロセスばらつき

- 電力管理

- 高性能なアナログ回路

いずれも従来から重要視されてきた事柄ではある。ただし、40nm世代では、これらの問題は従来とは異なる様相を帯びることになる。以下、それぞれについて順に説明していく。

FPGAとASICの製造プロセス

表Aは、ASICの設計/製造に用いられたプロセス技術ノードの割合を年ごとに示したものである。これは米Gartner社がまとめたものをベースとしており、2007年までは実績値で、2008年以降は予測値となる。

つい最近まで、最も多く使用されるプロセスノードは0.13μmプロセスであった。0.13μmプロセスは多くの用途に対して十分な集積度と性能を提供しており、開発コスト(NREコスト)がほどほどの金額で済むからだ。これに対して90nm(0.09μm)以降のプロセスノードでは開発コストと開発リスクが増大し、消費電力に留意した設計が必要になる。このため、多くのASIC設計プロジェクトにとって、90nm以降のプロセスノードでは、投資対効果(ROI)のバランスをとることが難しい。

表Aの右端の列には、各プロセスノードにおけるASICの開発費用(Altera社による推定値)を示した。この開発費用は、マスクコスト、設計コスト、テストコスト、ソフトウエア開発コスト、人件費などから成る。プロセスノードが微細化の方向に進むに従い、開発費用が急激に増加していることがわかる。ここで忘れてならないのは、開発費用とともに開発リスクが高まり、開発期間が長期化していることである。

過去、FPGAのプロセスノードとしては、ASICのプロセスノードよりも古い世代のものが使われていた。ところが、現在ではASICよりも新しいプロセスノードがFPGAで使われるようになった。このまま行くと、FPGAはプロセスノードで3世代ほどASICに先行することになる。

45nmノードまたは32nmノードのFPGAは、0.13μmノードのASICに比べ、コスト、集積度、性能の面ではるかに勝る。FPGA用のソフトウエア開発ツールに投資すれば、半導体ユーザーは最新のプロセス技術の恩恵にあずかれる。FPGAはプログラマブルなので、特定の顧客向けであるASICとは異なり、数多くの半導体ユーザーが利用できる。IC企業にとっては、投資対効果が安定しているので新しいプロセス技術に投資しやすい。開発期間やコスト、性能、消費電力、開発リスク、開発費用などの面で、ASICからFPGAへの乗り換えが進むケースが増えていくだろう。

脚注:

※1…(編集部注)本稿の著者らが所属するAltera社は製造工場を持たないファブレスの半導体ベンダーである。同社は、半導体の製造を請け負うファウンドリ企業が開発した製造プロセスを利用することを前提としてFPGA/PLDの新製品を設計している。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「通信エラー」の原因を追う――搬送機器のコントローラーを修理【前編】

- ARM台頭にルネサス誕生……時代に翻弄され続けた日立「SuperH」

- Ankerがイヤホン用AIチップ、NORフラッシュベースCiM処理

- 「解読不可能」を破る量子コンピュータ――今から始める暗号セキュリティ

- Intelが「Core Series 3」モバイルプロセッサ、エッジ機器向けに

- フェライト(3) ―― 電子部品としてのフェライト

- アルミ電解コンデンサー(1)―― 原理と構造

- AI/HPC用ガラスビア向け 低収縮特性の銅ナノペースト

- SDVとは? 定義や課題、時代に合わせたモビリティDX戦略の重要性

- 次世代車載向けセキュリティコントローラー

写真1 40nmプロセスで開発したFPGAチップの写真 40nmプロセスでは複雑化とチップの大型化が進み、設計コストが増加する。そのため、従来とは異なる開発手法が要求される。

写真1 40nmプロセスで開発したFPGAチップの写真 40nmプロセスでは複雑化とチップの大型化が進み、設計コストが増加する。そのため、従来とは異なる開発手法が要求される。