DRAMアクセスの高効率化を図る:マルチメディアSoC設計の要(2/2 ページ)

インターコネクトの構成

DRAMコントローラに、アクセス要求に関するすべての情報を伝達する方法は、個々の要求元ブロックの要件に基づくインターコネクト構造を合成することである。この場合の合成は、RTL(Register Transfer Level)記述からゲートレベルのネットリストを生成するという意味ではなく、ある抽象レベルから別の抽象レベルへの変換という意味でとらえてほしい。例えば、DRAMの動作の最適化を支援するための属性を含んだ高レベルなアーキテクチャ記述を基に、自己タイミング型のインターコネクト構造を自動化ツールで合成するといった方法をとる。

このような手法で合成されたインターコネクトは、要求元のIPコアを識別する情報を伝送することができるだろう。また、要求元のプロトコルがその識別機能を明示的にはサポートしていない場合でも、識別が可能となる。例えば、AHBイニシエータは明示的な識別機能を持たないが、インターコネクトを合成する際にSID(Source Identification:ソース識別情報)機能を割り当てれば、要求元を判別できる。インターコネクトがAHBイニシエータからDRAMコントローラへの要求の伝送時にSIDを伝送するようにすれば、DRAMコントローラが制御アルゴリズムを用いることでアクセス効率を向上させることができる。

もともと識別フィールドを持つようなプロトコルであれば、そのSID情報をそのままDRAMコントローラに伝送すればよい。また、設計者がシステムレベルの優先度や要求元に関するそのほかの情報も含めたいと考えている場合には、インターコネクトを合成するプロセスにおいて、そうした情報を付加するためのオプションのフィールドを付加する。

合成によって自己タイミング型の通信ネットワークがインターコネクトとして生成される場合、そのデータ転送レートはDRAMよりもずっと高くなるはずだ。そもそも、DRAMへのパスには多くのトラフィックが集約されるため、高速なインターコネクトが利用できれば、DRAMへのすべての要求を配線における最大の速度で伝送することができる。また、自己タイミング型の通信ネットワークであれば、クロックエッジを待つことなく、すべての要求ができる限り迅速にDRAMコントローラに伝達されることとなる。

さらに、インターコネクトは完全に連続的でなければならない。システムは、イニシエータからの長い要求を、その開始形式にかかわらず、変更することなくDRAMコントローラへと伝送しなければならない。加えて、インターコネクトにおいて情報を変更することがあってはならない。

一方で、イニシエータが要求を変更しなければならない場合が存在する。例えば、DRAMコントローラへの大容量のデータの書き込みに対応するために、書き込み要求時のバーストチョッピングを実装しようとシステム設計者が考えた場合などがこれに当たる。ターゲットのDRAMが処理できるバーストサイズに合わせて要求ストリームを変更する処理は、イニシエータで実施しなければならない。しかし、この方法においても、バーストチョッピングの決断を下すのはインターコネクトであってはならない。インターコネクトの役割は、あくまでも、イニシエータが送信する要求をそのまま伝送することである。

合成の際は、インターコネクトとともに、アダプタも生成する必要がある。アダプタとは、エンドポイントの要求を処理するロジックのことで、そのほかに再順序付け機能を備える。このアダプタによって、例えばAHBとOCPの両方のイニシエータを含むような混成システムを構成できる。さらに、再順序付けを完全にサポートすることで、DRAMコントローラを最大限に効率的に動作させることが可能である。

再順序付け機能を備えたアダプタは、AHBを用いるようなエンドポイントに対する要求の順序を管理する。例えば、DRAMコントローラが効率向上のためにある要求の順序を変更した際、エンドポイントからは常に順序どおりであると見えるように管理するのだ。

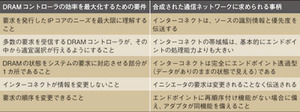

表1に、DRAMの効率に関する問題と、正しいプロセスによって合成されたインターコネクトによるそれらの問題への対処方法をまとめておく。

2Dブロック転送

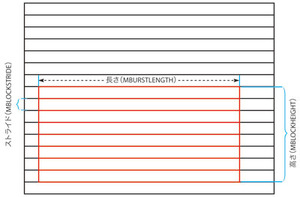

2Dブロック転送は、DRAMのアクセス効率を向上できる機能の一例である。この転送では、イニシエータからインターフェースを介しインターコネクトを経て受信ターゲットへと情報が渡される。つまり、1つの要求に基づき複数のデータをやり取りするSRMD(Single Request Multiple Data)コマンドの一種だ。現時点でこの機能を正式にサポートする唯一のプロトコルであるOCPのバージョン2.2(以下、OCP 2.2)において、2Dブロック転送は「MBurstSeq=BLCK」と呼ばれるバーストアクセス要求となる。この要求では、図2のように開始アドレスと幅(2D転送の場合は各行の長さ)に加え、高さ(ブロック内の行数)とストライド(1行の開始点から次の行の開始点までのオフセット)の情報が送信される。

多くの場合、受信側はDRAMコントローラだが、ビデオ処理システムでは書き込みのみが行われるビデオディスプレイであることもある。この受信側では、特殊なハードウエアが2Dバースト要求を受け取り、要求パラメータを保存する。このハードウエアが、ストライドに基づいてある行から次の行へのインクリメント処理の管理を行い、また高さに基づいてバーストの末尾を判断する。

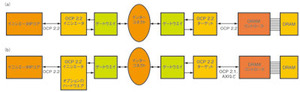

図3は2Dブロック転送の2つの実装方法を示したものである。この例では、図3(a)と(b)のいずれにも、インターコネクトとしてSilistix社のツールによって合成した自己タイミング型の通信ネットワークを用いている。また、いずれもイニシエータからDRAMコントローラへの単一のパスを示している。ただし、実際のイニシエータは、ほかのエンドポイントやほかのパスなどにもアクセスする必要がある。

図3(a)では、MBurstSeq=BLCKバーストタイプのコマンドを発行するOCP 2.2対応のイニシエータから、同様にOCP 2.2に準拠したMBurstSeq=BLCKコマンドを受信可能なDRAMコントローラまでが、データルートの主幹を成している。DRAMコントローラには、ストライドと高さに応じたバーストを格納して操作するためのレジスタとロジックがある。この図3(a)のような実装では、重要な各エンドポイントにおけるアダプタは、OCP 2.2に準拠したものでなければならない。

イニシエータは、MBurstSeq=BLCKを受信すると、その要求をインターコネクトが用いる内部フォーマットに応じた形で格納し、そのほかのフィールドとともに変更することなく、ターゲットのアダプタへと伝送する。ターゲットのアダプタでは、内部フォーマットデータから情報を取り出し、イニシエータから受信したとおりの状態でOCP 2.2のバスにそのデータを供給する。DRAMコントローラからのデータを受信すると、ターゲットのアダプタは、そのデータを元の要求と関連付けた上で、コマンドに対する応答としてイニシエータに返す。

図3(b)は、要求を発行するのは同じようにOCP 2.2対応のイニシエータだが、DRAMコントローラはOCP 2.2に非対応であり、MBurstSeq=BLCKバーストタイプをサポートしない場合の例である。例えば、AXIインターフェースやバージョンの古いOCP、あるいは標準プロトコルではなくオリジナルのインターフェースを備えたユーザー固有のコアを用いるケースであるが、いずれの場合においても、実装する回路の動作は同じである。

イニシエータはOCP 2.2のMBurstSeq=BLCKを受信し、ターゲットがOCP 2.2に対応していないと判断すると、ストライドと高さの情報などをオプションのハードウエアに保存する。システム設計者が、OCP 2.2に基づいたイニシエータからのMBurstSeq=BLCKをサポートしたい場合、インターコネクトを合成する際には、このオプションのハードウエアを合成するように指定することになる。

イニシエータは、2Dブロック転送を適切な数の従来型のバースト転送に分解し、インターコネクトを介してDRAMコントローラへと発行する。このようにDRAMコントローラが非標準のインターフェースを使用している場合、インターコネクトはDRAMコントローラに対し、このタイプのバースト要求が複数送られていることを警告することができる。また、2Dバーストをターゲット側で分解し、自動的にエンドポイントのDRAMコントローラに伝送することも可能である。DRAMコントローラが用いるアルゴリズムによっては、このような情報を付加するだけでMBurstSeq=BLCKバーストタイプの処理効率が向上する可能性がある。OCP 2.2に対応したイニシエータが、OCP 2.2に準拠/非準拠の両方のエンドポイントに2Dブロック転送を発行する必要があるようなシステムにおいても、同じ方法が適用できる。

DRAMへのアクセスを効率化するには、要求の性質とエンドポイントの種類に関する情報を基に、2Dブロックコマンドを直接受信可能なエンドポイントと、オプションのハードウエアの使用が必要となるエンドポイントとをイニシエータが識別できるようにする必要がある。この方法により、OCP 2.2のMBurstSeq=BLCKバーストタイプに対する2種類の処理に対応するためにハードウエアが少しだけ増加するものの、複数のインターコネクトが混在するシステムを高効率に管理することができるだろう。

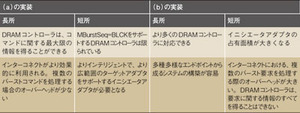

図3に示した2つの実装方法を評価する際には、設計チームはさまざまなトレードオフについて検討する必要がある。表2に、図3(a)、(b)の2Dブロック転送に関連するトレードオフ項目をまとめておく。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「通信エラー」の原因を追う――搬送機器のコントローラーを修理【前編】

- ARM台頭にルネサス誕生……時代に翻弄され続けた日立「SuperH」

- Ankerがイヤホン用AIチップ、NORフラッシュベースCiM処理

- 「解読不可能」を破る量子コンピュータ――今から始める暗号セキュリティ

- Intelが「Core Series 3」モバイルプロセッサ、エッジ機器向けに

- フェライト(3) ―― 電子部品としてのフェライト

- アルミ電解コンデンサー(1)―― 原理と構造

- AI/HPC用ガラスビア向け 低収縮特性の銅ナノペースト

- SDVとは? 定義や課題、時代に合わせたモビリティDX戦略の重要性

- 次世代車載向けセキュリティコントローラー