ICの電力管理、最大の課題は検証手法(2/3 ページ)

パワーゲーティングの問題点

電圧アイランドを設けて回路ブロックの隔離が行えるのであれば、非動作時にはその電圧アイランドへの電源を遮断するというのが自然な発想である。しかし、この概念、すなわちパワーゲーティングは、検証チームに新たな一連の問題を投げかけた。

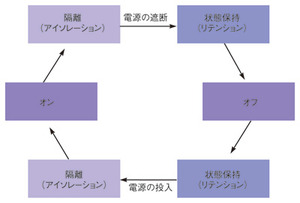

当然のことながら、パワーゲーティングの対象とするブロックの電源が遮断されているときも、動作中のほかのブロックは正しく機能しなければならない。加えて、電源をオンにしたりオフにしたりするためには、入力と出力の隔離、ブロックの内部状態の保存、そのブロックとほかの回路との再接続に伴う細かい調整が必要となる(図1)。

米Freescale Semiconductor社の検証チームを率いるPrashant Bhargava氏は、「われわれはパワーゲーティングを適用した回路を4つのステップで検証している。まず、電源の遮断シーケンスを検証する。次にブロックの電源をオフにした状態でそのほかの回路の動作を検証する。適切に隔離が行えており、正しい状態を保持しているかどうかを確認するのが主な目的だ。その後、電源の投入シーケンスを検証する。そして最後に、電源がオンになっている状態でブロックを検証する」と説明する。

ほかの多くの企業と同様に、Freescale社も、米Cadence Design Systems社らが策定したCPF(Common Power Format)ファイルを用いて電源管理の意図を把握できるようにしている。「CPFファイルによって、ゲーティング信号、ゲーティングが適用されるブロック、電源管理回路、電源を投入するブロックと遮断するブロックとの間のインターフェース、ブロックを隔離するためのコマンド、レベルシフターの位置を明確にする」とBhargava氏は述べる。CPFファイルは電力管理の設計意図を定義するための中心的な存在であり、設計の下流工程において、各種ツール(主にCadence社のツール)とともに使用してシミュレーションや合成などの作業に活用することができる。

CPFファイルは電力設計の集中管理の手段として有望かもしれないが、大きな問題も抱えている。1つは、CPFファイルを自動的にチェックする方法が存在しないことである。米Staccato Communications社のデジタル設計担当ディレクタを務めるSam Leung氏は、「合成によって得られた結果が要求どおりであるかどうかを検証する作業は、いまだに目視で行っている」と語っている。特にパワーゲーティングでは、正しい構造が実際に回路の中に存在するかどうかを検証チームが手作業でチェックする必要がある。「入力と出力が非常に多く、手作業でチェックしなければならない関連項目数が大量にあるため、ミスが生じてしまう」とLeung氏は述べる。

CPFまたはUPF(Unified Power Format)ファイルのチェックが終わったら、続いては回路を検証しなければならない。その現状について、Leung氏は「CPFファイルからデータを取り出し、電力管理用のテストベンチを生成するツールが存在しない」ことを嘆く。同氏は「電力管理機能の動作を検証するために、テストベクターを作成する必要がある。その検証は、ゲートレベルではなく、機能レベルのみで実施すればよい。複数の電力ドメインをまたがる信号の検証が注目すべき事柄だ。何かがどこかでもれているなら、それを見つけ出す必要がある」と語る。

インドeInfochips社の設計マネジャであるNilesh Ranpura氏も、検証作業の体系化を図るためにCPFを利用している。Ranpura氏は、「検証に当たっては、電力制御に用いるステートマシンのシーケンスを明確にし、各状態にどのような電圧の組み合わせがあるのかを把握しなければならない。この作業は自動的に実施することはできないし、すべてのシミュレーションツールからCPFファイルのデータにアクセスできるわけでもない。それでも、われわれはCPFファイルを利用することによって、検証時間を約40%短縮することができた」と、その効果を説明する。

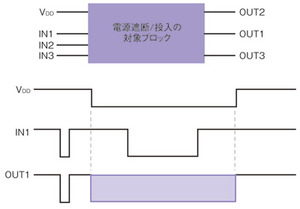

Ranpura氏が指摘する問題の1つは、ブロックの電源をオンにしたりオフにしたりすると、システムの信号の状態が、一般的なシミュレーションツールで提供されている1、0、Z、Xだけでは表現できなくなることである(図2)。「Boolean値を用いたアサーションを使用する場合、誤った判定が行われないような抑制が必要となるケースが生じる」とRanpura氏は述べる。

IBM社のFloyd氏も、シミュレーションにおいて1、0、Z、X以外の状態が必要になるという点に同意している。「パワーゲーティングを使用し始めたころは、未知の状態を扱わなければならない状況が増えたため、消化不良を起こしていた。現在は代替手法を積極的に開発しているところだ。基本的には、ツールによって、パワーゲーティングの対象となるドメインがデータを破損しないことを検証することができる。これは非常に画期的なことだ」と同氏は語る。

シーケンサが設計意図に沿って実装されていることが確認できたら、続いては入力される信号の論理だけでなく、電圧とタイミングが適切か否かを検証しなければならない。「互いに接続されたブロックの電源をオンにしたりオフにしたりする場合、レベルシフターのシーケンスが正しいことを検証する必要がある。設計意図と正確に一致させなければ、膨大な数のエラーが生じ、それらの原因を突き止めるのは非常に困難な作業になってしまう」とRanpura氏は述べる。

また、論理レベル以外での問題も生じる。オランダNXP Semiconductors社のマイクロコントローラ設計マネジャであるAvindt Chopra氏は、「パワーゲーティングにおいて、メモリーは扱いに注意を要するブロックだ。パワーゲーティングの対象にすることは可能だが、その場合、状態遷移を非常に注意深くシミュレーションする必要がある。例えば、電圧の変更に伴うメモリーブロックへの突入電流のモデリングなどが重要になる」と述べる。

バスも注意を要する重要な部分である。STMicroelectronics社のDucousso氏は、「IPブロック全体をゲーティングする場合、そのブロックがシステムバスに接続しているならば、遷移中にバスインターフェースが電気的に“きれいな”状態であるようにしなければならない」と述べる。

Ducousso氏はもう1つ、バスに関する興味深い問題を指摘した。それは次のようなことである。

「ペンディング中のバス要求が、あるブロックの電源を遮断すると、非常に大きな問題につながる。おそらくそのほかの多くのケースにおいても、システムの電源を遮断する前に確認すべき状態は、ブロック内で完全に閉じたものであるとは限らない。そのブロックとハンドシェイクする隣接したブロックや、遠くに位置するバスアービタについても確認しなければならないかもしれない。もう1つ確認しなければならない重要なことは、電源シーケンスにおけるDRAMコントローラの状態だ。電源の遷移中に誤って生じた書き込みサイクルによってメモリーデータが破損してしまった場合、その原因を突き止めるのは、ほぼ不可能だと言える」。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「通信エラー」の原因を追う――搬送機器のコントローラーを修理【前編】

- ARM台頭にルネサス誕生……時代に翻弄され続けた日立「SuperH」

- Ankerがイヤホン用AIチップ、NORフラッシュベースCiM処理

- 「解読不可能」を破る量子コンピュータ――今から始める暗号セキュリティ

- Intelが「Core Series 3」モバイルプロセッサ、エッジ機器向けに

- フェライト(3) ―― 電子部品としてのフェライト

- アルミ電解コンデンサー(1)―― 原理と構造

- AI/HPC用ガラスビア向け 低収縮特性の銅ナノペースト

- SDVとは? 定義や課題、時代に合わせたモビリティDX戦略の重要性

- 次世代車載向けセキュリティコントローラー