40/100GbEが抱えるテスト技術の課題:対応製品の登場で見えてきた(1/2 ページ)

実用化に向けて着々と標準化が進む40/100GbE。すでに多くのメーカーがこれらの規格に対応する製品を開発し、販売を開始している。そうした製品のテストには、10GbEに使われている技術を応用できるが、一部では新しい方法や装置が必要となる。本稿では、特にテストに関して、新たに要求されるであろう事柄についてまとめる。

テスト技術の早期確立が必須

インターネットやデータセンターのユーザーは、音声やデータ、映像をより多く、より早く伝送するために、帯域幅の拡大を絶えず求めている。とどまることのないその要求により、今や10ギガビット/秒(Gbps)の伝送容量でも不足しつつある。2008年3月に開催された『OFC/NFOEC(Optical Fiber Communication Conference and Exposition/National Fiber Optic Engineers Conference)』の参加者らによると、データセンターやコアネットワークには、より高速なリンクが必要であるという*1)。その当時、IEEE P802.3baのイーサーネット作業部会は、40Gbpsおよび100Gbpsのイーサーネット(以下、40GbE、100GbE)のアーキテクチャを定義する規格を策定中であった*2)。

一方、IEEE P802.3baの策定作業がまだ進行中であるのにもかかわらず、世界中の技術者らは、同規格に準拠する製品をすでに開発し始めている。そのため、こうした製品のテスト方法の早期確立が求められている。IEEE P802.3baに関するテストの大部分は、10ギガビットイーサーネットで確立された技術を用いて実施されるが、一部のテストには新しい装置と手法が必要となるからである。

アーキテクチャの概要

米Force10 Networks社のシニアサイエンティストで、IEEE P802.3ba作業部会の会長を務めるJohn D'Ambrosia氏は、同規格の詳細部分を策定するチームを統括している。詳細はまだ確定していないが、IEEE P802.3ba作業部会は、全体的なアーキテクチャと、アーキテクチャのプロトコルサブレイヤー(副層)、サブレイヤーの機能の定義をすでに終えているという*3)。

図1は、40Gbpsおよび100Gbpsの光ネットワークにおけるアーキテクチャを簡略化して表したものである。2つのアーキテクチャにわずかな違いはあるが、ICメーカーは1つの部品に両者を実装することができる。

光ネットワークについて、IEEE P802.3baは、PCS(Physical Coding Sublayer:物理符号化副層)、PMA(Physical Medium Attachment:物理媒体接続)サブレイヤー、PMD(Physical Medium Dependent:物理媒体依存)サブレイヤーを定義している。40/100Gbpsの伝送システムを実装する際には、10Gbpsの光ファイバの物理層(PHY)リンクを利用できる。将来的には、同じアーキテクチャで25Gbpsのレーンを4本用いた100Gbpsのリンクをサポートする予定だ。また、IEEE P802.3baは、銅線ケーブル接続用に別の2つのサブレイヤーも定義している。

PCSは、集約された40Gbpsまたは100Gbpsのデータストリームに対して64b/66b符号化を施し、66ビットのデータブロックを生成する。そして、これらのブロックを、40Gbps伝送の場合は4本の、100Gbpsの場合は20本のレーン上に送信する。D'Ambrosia氏は、「レーンを20本にしたのは、20という数字が1、2、4、5、10で割り切れるからだ」と説明する。PCSは4レーンまたは10レーンに対応する予定だという。20本のPCSレーンのそれぞれには、レーンを識別して各ブロックのタイミング情報を提供するレーンマーカーが含まれている*4)。図2に、66ビットのブロックがPCSレーン内を移動する様子を示した。ブロックはストライピング処理によって分割され、ラウンドロビン方式で各PCSレーンに分配される。

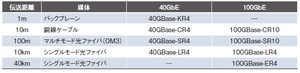

PMAサブレイヤーは、PCSレーンの本数と物理層が必要とするレーン数をマッチングさせる。40Gbpsの場合、同サブレイヤーは4本のレーンを使用する。一方、100Gbpsの場合には、20本のXLAUI(40Gbps Attachment Unit Interface)レーンを10本のXLAUIレーンに、または20本のCAUI(100Gbps Attachment Unit Interface)レーンを10本のCAUIレーンに変換する。PMDサブレイヤーは、物理媒体への最後のインターフェースとなる。表1に、各物理媒体とその伝送距離を示す。一般的に、40Gbpsはデータセンターで利用され、100Gbpsはコアネットワークで利用される。

IEEE P802.3baのアーキテクチャは 柔軟性が高く、シングルモード光ファイバにWDM(Wavelength Division Multiplexing:波長分割多重)を適用した、Long-ReachおよびExtended-Reachの光リンクをサポートする。WDMとは、波長の異なる複数の光信号を同時に利用することで、光ファイバ上の情報伝送量を増大させる方式である。Short-Reachのリンクでは、それぞれが異なるレーンを保有する複数の光ファイバを使用する。10Gbpsの信号を送受信するコンポーネントがすでに存在するため、40Gbps/100Gbpsの伝送システムの初期実装では、4本/10本の10Gbpsレーンを使用する。25Gbpsリンクを用いた4レーン実装(符号化により実速度は25.78125Gbpsになる)の登場にはまだしばらく時間がかかるが、通信事業者は、40km伝送向けとして、シングルモード光ファイバに4波長のWDMを使用する計画である*5)。

脚注

※1…Rowe, Martin, "OFC/NFOEC 2008: On to 100G," Test&Measurement World, Feb 27, 2008

※2…Rowe, Martin, "100-Gbps Ethernet is coming," Test&Measurement World, Dec 6, 2007, p.21

※3…D'Ambrosia, John, David Law, and Mark Nowell, "40 Gigabit Ethernet and 100 Gigabit Ethernet Technology Overview," Ethernet Alliance, 2008

※4…"Trends and Issues in Ultra-High-Speed Transmission Technologies," Anritsu, November 2008

※5…Suzuki, Toshihiro, "XLAUI/CAUI Jitter Tolerance Test Requirement Proposal," Comment 199 from the November 2008 Plenary Meeting, IEEE P802.3ba 40Gb/s and 100Gb/s Ethernet Task Force, November 11 to 13, 2008

Copyright © ITmedia, Inc. All Rights Reserved.