アサーション活用の手引き:その基本から、記述ノウハウ、フォーマル解析への展開まで(2/5 ページ)

メリット、デメリット

アサーションを利用した検証であるABVには、メリットだけでなく、当然、デメリットもある。デメリットが存在するとしても、結果的にはそれを超えるメリットがあるのだが、まずはデメリットについて紹介した上で、メリットとその大きさについて説明する。

まず、ABVのデメリットとしては、以下のような事柄が挙げられる。

- アサーション言語を習得するのに時間を要する。各検証ツールに組み込まれているアサーションライブラリやOVL(Open Verification Library)を利用する場合でも、その使用方法を学ぶ必要はある

- アサーションを記述する時間が追加で必要となる。限られた開発期間の中で新たな作業を追加するのは困難である

- アサーション自体をデバッグしなくてはならないこともある

- ダイナミック検証におけるアサーションの追加は、パフォーマンスの低下を確実に引き起こす

一方、ABVのメリットは以下のとおりである。

- 記述した仕様自体の正しさを、ツールによって正確に検証できる。アサーションの記述は、仕様をブレークダウンする作業である。アサーション言語はコンピュータ言語なので、あいまいな記述は許されない。アサーションを記述/検討する工程において、仕様に対する深い理解、あいまいな点の把握、問題の指摘が行える

- 検証では、シミュレーションの実行時間よりもデバッグに費やす時間のほうが長くなることが多い。結果として、プロジェクト全体を通してみると、アサーションによって、デバッグ時間を短縮することができる

- アサーションを利用して、後述するフォーマル解析を実施することにより、完全な検証が行える。フォーマル解析ではテストベンチの開発が不要なので、RTLのコーディング後すぐに検証を開始できる。そのため、検証の生産性の向上と、完全な検証による設計品質の向上が実現可能である

- アサーションを活用できるということは、自らが検証技術力を有しているということを意味する。現在、検証へのニーズがますます高まっている半面、検証担当者が設計担当者に対して不足しているという実情がある。そのため、検証技術力を持つ技術者の価値は高い

図2に示したのは、従来のフローとABVのフローを工数の観点から比較したものである。この図は、ブロック設計のフェーズでアサーションを利用することを前提としている。このような条件において、アサーションのメリットをピンポイントで理解するのは難しい。ブロック設計のフェーズではアサーションを挿入する工数が追加されるし、シミュレーションのパフォーマンスが落ちて実行時間が延びるからである。

では、ABVのメリットとは、端的に言うとどういうことなのか。それは、以下のようにまとめることができる。

アサーションのいちばんのメリットは、プロジェクトの早期の段階で確度の高い検証を行うことにより、より早く安定した設計が得られることである

すなわち、「工数の削減」といったピンポイントのメリットではなく、プロジェクト全体で見た場合のメリットが大きいということだ。

これだけ覚えれば十分

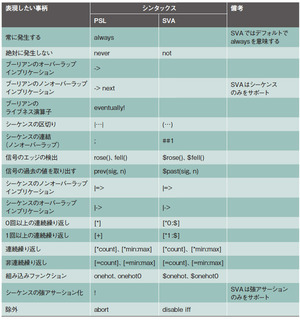

限られた開発期間内に、新たな言語を習得するのは困難なことである。アサーション言語には多くのシンタックスが用意されているが、そのすべてを覚える必要はない。アサーションを用いて検証できる項目の80%は、アサーション言語が備えるシンタックスの20%で表現可能だと言われている(表1)。また、使用するシンタックスを制限することで、記述の理解が容易になり、再利用性が高いアサーションを記述できるとも言える。

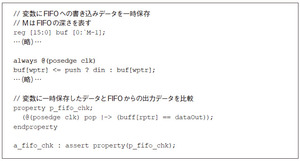

この20%のサブセットで表現できない検証項目については、アサーションの記述を補助するためにVerilog HDLやVHDLといったHDL(ハードウエア記述言語)を利用することで対応できる。例えば、あるイベント数をカウントしたい場合には、HDLでカウンタを記述し、そのカウント値を、限られたシンタックスで記述したアサーションの中で参照するという方法をとればよい。また、値を記憶するためのメモリー変数をHDLで用意しておき、それをアサーション記述中で比較するといったことも可能だ(リスト3)。

なお、アサーションで使用する構文を制限することによって、本当に必要なことが記述できなかったり、間違ったアサーションを記述してしまったりするようでは本末転倒である。しかし、慣れ親しんだHDL記述をうまく利用すれば、豊富な表現が可能になることは理解しておきたい。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング