ホールド時間の延伸方法:Signal Integrity

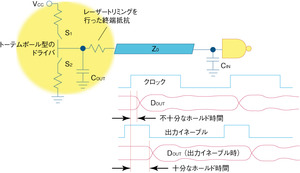

図1の左上部に示したのは、CMOSドライバの等価回路である。この回路において、スイッチS1を閉じてS2を開き、出力をハイにしたとする。その後、伝送ラインの状態が安定するまでしばらく待つ。負荷にはDCパスはなく容量成分しかないので、定常状態での電流はほぼゼロになる。完全にゼロにならないのは、ドライバやレシーバ、あるいは伝送ライン自体にわずかなリーク電流が存在するからである。状態が安定した後にスイッチS1を開き、ドライバの出力をハイインピーダンス(スリーステート出力)にすると、伝送ラインのレベルはハイにとどまる。しかし、リーク電流が存在するので、レベルは徐々に低下していく。

実際の回路では、スリーステート出力の状態で確実にハイに保持される時間は、数nsのレベルをかなり超えることもある。ドライバがスリーステート出力機能を備えている場合、それがデータを短時間保持する一種のダイナミックメモリーとして働くことから、ドライバのホールド時間を延伸することに利用できる。その働きはDRAMと同じ原理に基づくので、確実性の面でもDRAMと同等である。この働きを利用する上で難しいのは、最悪条件でのリーク電流を確実に把握することだ。ドライバ回路のリーク電流は温度に対して指数関数的に増大するので、リーク電流の試験は、実使用時の温度で実施しなければならないことに注意しておきたい。

スリーステート出力機能の利用が効果的な例を示そう。ここでは、互いに同期したマスターとスレーブの2個のラッチがともに同じ10MHzのクロックで動作しているケースを考える。一方の出力DOUTから他方にデータが送られ、各ラッチとも、クロックの立ち上がりエッジで動作するものとしよう。最新のCMOSロジックを用いることを前提にすると、このクロック速度ではセットアップ時間には十分な余裕があるが、ホールド時間にはあまり余裕がない。特に、送信側の素子が受信側の素子よりもはるかに高速である場合などには必ずしも十分ではない。受信側のラッチに必要なホールド時間は、送信側のラッチで保証される値では不十分なことがあるのだ。このようなケースでDOUTに対するホールド時間を延伸する方法としては、以下のようなものがある。

- 送信側のラッチへ供給するクロックを遅らせる

- データ伝送のパスに、ディレイラインを直列に挿入する

- 送信側のラッチにおいて、各クロックエッジの前後の短時間だけスリーステート出力とし、受信側のラッチに必要なホールド時間が成立するまで出力データの遷移を止める

スリーステート出力にする際には、伝送ラインのレベルが完全に安定するまで待つ必要がある。伝送ライン上に顕著な反射波が存在するときにスリーステート出力にすると、それらの反射波がドライバの容量COUTと負荷の容量CINで反射を繰り返し、共振のような状態でリンギングが生じる。このリンギングの残留成分は、クリティカルなタイミング期間に長く残ることにもなる。

この種のリンギングは、たとえ終端抵抗が完全にレーザートリミングされたポリシリコン抵抗であったとしても、信号源終端(ソースターミネーション)では防止できない。スリーステート出力の期間はスイッチが開いており、終端抵抗が伝送ラインと低インピーダンスの電源配線とをつなぐことができないからだ。つまり、この終端抵抗が有効に働くのは、ドライバがハイ、ローのいずれかを出力している(出力イネーブル)ときだけだ。このような理由により、伝送ラインのレベルが安定するまで待った後に、スリーステート出力に設定しなければならないのである。

<筆者紹介>

Howard Johnson

Howard Johnson氏はSignal Consultingの学術博士。Oxford大学などで、デジタルエンジニアを対象にしたテクニカルワークショップを頻繁に開催している。ご意見は次のアドレスまで。www.sigcon.comまたはhowie03@sigcon.com。

Copyright © ITmedia, Inc. All Rights Reserved.