高速アナログ回路の基板設計手法:ギガサンプルADCのリファレンスボードに学ぶ(1/2 ページ)

複数のレイヤーから成るプリント基板において、不整合、損失、歪、EMIを生じさせることなく、数百MHz以上の周波数信号を扱うのは難しい。しかし、基板設計に関するいくつかの原則に従えば、信号品質を維持しつつ、十分な性能を実現することができる。本稿では、筆者らがギガサンプルレベルの高速A-Dコンバータ(ADC)のリファレンスボードに適用した基板設計手法を紹介する。

信号品質の確保に向けて

一般に、扱う信号の周波数が数百MHzを超えるような用途では、プリント基板(以下、基板)としては4層以上のものが必要となる。通常、その基板にはバラン、チップコンデンサ、抵抗などの小型部品を実装するが、端子数が数百にも上るBGA(Ball Grid Array)を用いる場合、基板が8層未満になることはなく、一般的には10層以上にもなる。すなわち、基板上の最も端子数の多いデバイスにより、レイヤー数が決まるとも言える。

例えば、米National Semiconductor社の高速A-Dコンバータ「ADC10D1000」は、292端子のBGAパッケージで提供されている。この製品は、シングル入力では2ギガサンプル/秒(Gsps)、デュアル入力では1Gspsで動作し、10ビットの分解能を備える。また、この製品のリファレンスボードで使われているFPGA「Virtex-4」(米Xilinx社製)のパッケージは、668端子のBGAである。このように端子数が多いICを利用する場合、すべての端子にアクセスできるようにするためには、少なくとも8層の基板が必要となる。

複数のマイクロ波信号線、ノイズ耐性の低いアナログ信号線、高速FPGA、スイッチング電源などが混在する基板上で、ギガヘルツレベルのサンプルレートで動作するA-Dコンバータを用いる場合、偶然に頼って10ビットの性能を達成することはできない。本稿では、ADC10D1000のリファレンスボードに実際に適用した手法を基に、高速アナログ信号を問題なく扱うことが可能な基板設計のノウハウをまとめる。

基板の材料

まず最初に、基板の材料について検討する必要がある。米Park Electrochemical 社が提供するエポキシ基材「Nelco N4000-6」は、少ない損失と高い耐久性を必要とするケースに適している。同製品の誘電率は従来型のFR4基材と同程度だが、高周波性能に優れている。また、テフロンなどのマイクロ波用誘電体基材のように、最上層と最下層のみで用いるものではなく、すべての層で使用することが可能である。 ADC10D1000のリファレンスボードは、10層基板とした。

National Semiconductor社は、同一のボードをFR4基板でも製造している。信号損失が問題にならない用途では、こちらのほうが適しているケースもある。FR4のほうが損失正接が高いため、整合がそれほど困難ではない。また、FR4は伝送線で反射を生じ得る信号のほとんどを吸収し、反射係数(S11パラメータ)の面で優れている。ただし、伝送線の長さは3インチ(約7.6cm)以下でなければならない。対FPGAのデジタルインターフェースの周波数は 2GHz未満なので、Nelco N4000-6とFR4との間にあまり差はない。

理想は同軸ケーブル

高周波の信号に対しては、伝送線の整合が重要になる。同軸ケーブルでは、中心の導体から周囲のグラウンドシールドまでの距離が均一なのでインピーダンスは一定である。これにより速度係数も一定となり、同軸ケーブルを伝送する信号の速度は均一となる。言い換えれば、同軸ケーブルでは、信号に対するインピーダンス整合が最良となる。基板上の限られた面積に複数の信号線が存在する場合に、高性能の伝送と絶縁を実現するには、インピーダンスが50Ωで外径 23mil(0.58mm)の超極細同軸ケーブルを使用するとよい。この同軸ケーブルを基板の表面に積層するのである。

このような同軸ケーブルを使えるなら理想的だが、この手法は、主に限られた面積の中で数多くの高周波信号を扱わなければならないハイエンド機器、軍事関連機器、航空宇宙機器などの用途以外では、コストの面から選択肢とはなり得ない。そのため、民生機器の多層基板では、マイクロストリップライン(表面型)かストリップライン(埋め込み型)が最良の解となる。

これらの利用を考える場合には、レイアウトを開始する前に、基板メーカーからスタックアップデータを入手する必要がある。このデータから、マイクロストリップラインの伝送線と、ストリップラインの伝送線の両方に対する整合インピーダンスの大きさがわかる。米DDI社をはじめとする多くのメーカーがスタックアップデータを提供している。

マイクロストリップラインの限界

マイクロストリップライン*1)の基本的な原理は、線路のインダクタンスを線路のキャパシタンスで割り、その平方根を計算することで、インピーダンスが決まるというものである。実際には、配線(トレース)の幅や厚さなどをパラメータとしてインピーダンスを計算することになる。

上述したように、同軸ケーブルでは、その構造がもたらす均一な環境で信号を伝送することができるが、この構造を基板上のマイクロストリップラインで再現することはできない。それでも、マイクロストリップラインを使えば、何ら工夫を施していない任意のトレースを使用する場合よりも、良好な状態が得られる。ただし、繰り返しになるが、理想的な状態からは程遠い。トレースの幅を正確に計算し、グラウンドプレーンからのトレースの高さを慎重に検討しても、完璧な整合は得られない。この点について、マックスウェルの電磁方程式を持ち出すことなく直感的に説明してみると、まずトレースの上にある誘電体は空気であり、トレースの下にある誘電体とは大きな差がある。誘電率が約4のFR4を例にとると、誘電体の中の信号は、空気中の約半分の速度で伝送する。マイクロストリップラインを長い距離で利用することができないのはこのためである。

伝送線の長さが信号の1/4波長未満である場合、マイクロストリップラインを使用することができる。伝送線がそれよりも長い場合には、不整合が大きくなるため、マイクロストリップラインを使用することはできない。

なお、SMAコネクタを接続しなければならない場合や、テストポイントを基板表面に配置しなければならない場合、基板が2層しかない場合など、マイクロストリップラインを使用せざるを得ないケースもある。

■差動マイクロストリップライン

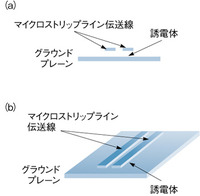

グラウンドプレーン上に配置した平衡差動信号線(差動マイクロストリップライン)を使用する方法もある(図1)。

2つの伝送線の電流は大きさが等しく逆向きで、外部の磁界を打ち消すことができる。その効果により、この種の伝送線は、単一の導体を使用するマイクロストリップラインほどにはグラウンドプレーンに依存しない。ただし、この差動信号線には、同軸ケーブルには存在する被覆が存在しない点に注意が必要である。

差動マイクロストリップラインにおいては、整合性に影響を与えるのはグラウンドプレーンだけではない。整合性は、対を成す伝送線に大きく依存する。この手法では、放射干渉信号と受信干渉信号の両方の影響を受ける。それでも、2層基板においては、この手法が堅牢な同軸ケーブルの次に最適な選択肢となる。ただし、通常のマイクロストリップラインを使う場合と比べて、ほぼ2倍の面積が必要になる。

脚注

※1…Wheeler, HA, "Transmission-line properties of parallel strips separated by a dielectric sheet," IEEE Transactions on Microwave Theory and Techniques, Volume 13, Issue 2, March 1965, p.172

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「通信エラー」の原因を追う――搬送機器のコントローラーを修理【前編】

- ARM台頭にルネサス誕生……時代に翻弄され続けた日立「SuperH」

- Ankerがイヤホン用AIチップ、NORフラッシュベースCiM処理

- 「解読不可能」を破る量子コンピュータ――今から始める暗号セキュリティ

- Intelが「Core Series 3」モバイルプロセッサ、エッジ機器向けに

- フェライト(3) ―― 電子部品としてのフェライト

- アルミ電解コンデンサー(1)―― 原理と構造

- AI/HPC用ガラスビア向け 低収縮特性の銅ナノペースト

- SDVとは? 定義や課題、時代に合わせたモビリティDX戦略の重要性

- 次世代車載向けセキュリティコントローラー