高速アナログ回路の基板設計手法:ギガサンプルADCのリファレンスボードに学ぶ(2/2 ページ)

ストリップラインの活用法

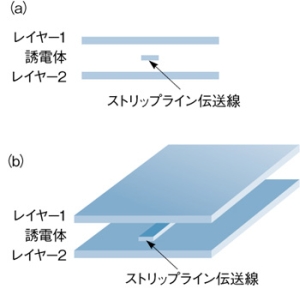

マイクロストリップラインの問題に対する解決策は、2つのプレーン間に挟まれたストリップラインを使用することである(図2)。この手法では、伝送線の周囲の誘電体が均一になる。しかし、導体のグラウンドリターンは均一にはならない。ストリップラインの場合、上面と下面のみにグラウンドリターンが存在する。すなわち、グラウンドのシールドが信号線の周りを360度囲む同軸ケーブルの最大の利点を備えているわけではない。

ストリップラインのもう1つの利点は、外界からのシールドが存在するため、干渉だけでなく、不要な放射信号からの影響を防げることだ。整合性はやや優れているものの、同軸ケーブルにはまったく及ばない。

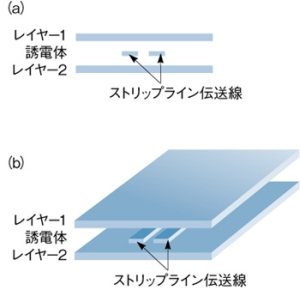

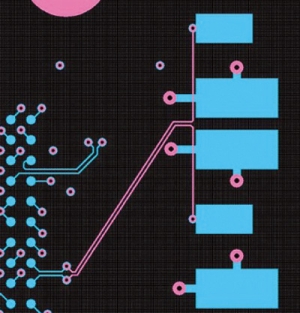

マイクロストリップラインの場合と同様に、平衡差動系を組んで、占有面積の増加と引き換えに性能を向上させるケースもある(図3)。これであれば、優れた整合性とEMI(電磁干渉)に対するシールド効果が得られる。同軸ケーブルには及ばないものの、ストリップラインをこのように使いこなすことが有力な解となる。

レイアウト上の注意点

ADC10D1000のリファレンスボードでは、インピーダンス整合が施された差動ストリップラインを使用した。各伝送線には、大きさが等しく向きが逆の電流が流れる。整合性は、誘電体の厚さ、基材の誘電率、平衡伝送線の間隔と厚さに依存する。これらの情報は、すべて基板メーカーから得ることができる。この手法を用いて、2つの電源またはグラウンドプレーンの間にストリップラインを配置することにより、EMIは測定できないほど小さく抑えられる。

ADC10D1000のリファレンスボードは、システム全体を完全差動系で構成している。チップのCMRR(同相信号除去比)だけでなく、外界からチップの入力へのインピーダンス整合も考慮している。

この手法の欠点は、複雑さが通常の方法(シングルエンド)の場合のほぼ2倍になることである。能動部品の総数が増えるため、熱雑音が増加し、それに伴って消費電力も増加する。

このリファレンスボードでは、その設計の初期段階において、設計者らは、バラン、アンプ、リレーをボードの外に配置することで入力インターフェースをできる限りシンプルにしようと考えた。また、リレーや不要なトレースは使用しなかった。そのような部品のすべてがボード全体の性能を低下させるからである。

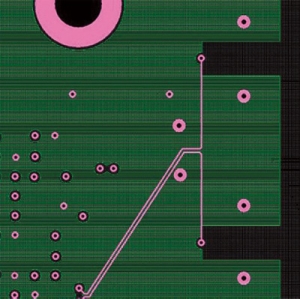

また、このリファレンスボードでは、以下の一般的な原則を適用することにより、優れた整合性を実現し、最大の帯域幅と最小のEMIを達成した。まず、A- Dコンバータの入力端子からは直ちにビアを配置し、伝送線は少なくとも1層下とするようにした。実際には、伝送線にはレイヤー3を用いることにした。すなわち、このレイヤーがストリップライン伝送線の中心となる。そしてレイヤー2と同4はACグラウンドとし、信号を外界の干渉からシールドするために使用した。差動ストリップラインを用いていることから、基板表面にあるシングルトレースの伝送線と比較して、長い距離においてもインピーダンスをよりよく維持することが可能になる。

正と負の入力電圧信号は、直ちに100Ωの平衡伝送線に接続している(図4)。性能を上げるためには、この処置が不可欠である。SMAコネクタ端では、ビアが表面レイヤー上に戻る。整合性を保つために、平衡伝送線をできる限り長くそのまま維持することが、1つの重要な原則である(図5)。

設計者が見落としがちなもう1つの重要な原則として、SMAコネクタから基板へのインピーダンスの整合がある。SMAコネクタ自体は50Ωに整合しているが、SMAコネクタ用の基板上のランディングパッドは整合していない。そのため、特に処置を施さなければ、周波数が1GHzを超えるレベルになると、ボード全体としての性能が劣化してしまう。ADC10D1000のリファレンスボードで使用するSMAコネクタは、SMAランディングパッドの幅が、50Ωのトレースの約4倍ある。50Ωのインピーダンスに整合させるために、レイヤー7をグラウンドプレーン(ACグラウンド)とした。また、SMAランディングパッドの下の緑色のグラウンドレイヤー(レイヤー2)は、ランディングパッドとともに大きなキャパシタを構成するので、除去する必要がある。さらに、このボードでは、SMAランディングパッドの下はレイヤー7まで導体が存在しない(レイヤー2から同6まで、導体を除去する)。

上記のレイアウト上の原則を適用することにより、優れた広帯域整合を実現することができる。

特性の確認

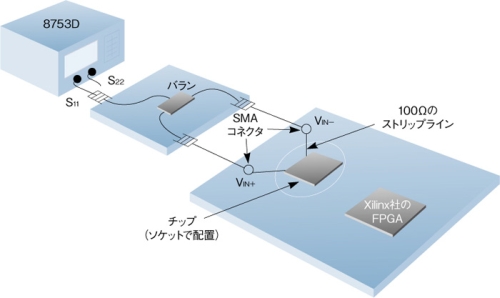

筆者らは、開発したリファレンスボードの評価を行った。評価装置としては、米Agilent Technologies社のネットワークアナライザ「8753D」を使用し、図6のような評価系を構成した。これにより、最大3GHzの周波数で−10dB未満の反射損失を達成することができる。

図7は、SMAランディングパッドの下のレイヤー2から同6を除去しない場合の評価結果(S11パラメータ)である。100Ωの終端抵抗で入力整合を行っており、この整合によって、最大1.5GHzの周波数にまで対応できている。一方、図8は、レイヤー2から同6を除去した場合の評価結果である。図7の結果に対して劇的な改善が見られ、最大3GHzの周波数にまで対応している。

図9は、ADC10D1000を配置した場合の入力整合の様子を表している。これを見ると、100MHzから3GHzにおいて、反射損失は最悪でも−12dB未満に抑えられている。

なお、レイヤー2から同6までで除去するグラウンドプレーンの正確な量については、議論が必要である。レイヤー2から同6は、それらを除いたとしても SMAランディングパッドのインピーダンスとなる。SMAランディングパッドのすべての磁界がレイヤー7で終端するわけではなく、レイヤー2から同6で終端するものもある。

2次元フィールドソルバープログラムを用いれば、多くの詳細部分を解析し、除去する量を決定することができる。フィールドソルバープログラムを利用できない場合には、SMAランディングパッドに関するデータを基板メーカーから入手する必要がある。基板メーカーは、サイズに関する正確な情報を提供してくれるはずだ。この情報も入手できない場合には、例えばレイヤー2から同6の各レイヤーにおいて、ストリップライン導体の3〜5倍の幅だけ除去するとよいだろう。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「通信エラー」の原因を追う――搬送機器のコントローラーを修理【前編】

- ARM台頭にルネサス誕生……時代に翻弄され続けた日立「SuperH」

- Ankerがイヤホン用AIチップ、NORフラッシュベースCiM処理

- 「解読不可能」を破る量子コンピュータ――今から始める暗号セキュリティ

- Intelが「Core Series 3」モバイルプロセッサ、エッジ機器向けに

- フェライト(3) ―― 電子部品としてのフェライト

- アルミ電解コンデンサー(1)―― 原理と構造

- AI/HPC用ガラスビア向け 低収縮特性の銅ナノペースト

- SDVとは? 定義や課題、時代に合わせたモビリティDX戦略の重要性

- 次世代車載向けセキュリティコントローラー

図2 通常のストリップライン 通常(シングルエンド)のストリップラインの断面図(a)と斜視図(b)。マイクロストリップラインよりは有利だが、十分に理想的なものであるとは言えない。

図2 通常のストリップライン 通常(シングルエンド)のストリップラインの断面図(a)と斜視図(b)。マイクロストリップラインよりは有利だが、十分に理想的なものであるとは言えない。 図3 差動ストリップライン 差動ストリップラインの断面図(a)と斜視図(b)。同軸ケーブルとまったく等価な効果が得られるわけではないが、優れた整合性とEMIに対するシールドを提供する。

図3 差動ストリップライン 差動ストリップラインの断面図(a)と斜視図(b)。同軸ケーブルとまったく等価な効果が得られるわけではないが、優れた整合性とEMIに対するシールドを提供する。 図4 入力信号部のレイアウト(その1) 正と負の入力電圧信号は、直ちに100Ωの平衡伝送線に接続している。

図4 入力信号部のレイアウト(その1) 正と負の入力電圧信号は、直ちに100Ωの平衡伝送線に接続している。 図5 入力信号部のレイアウト(その2) 整合性を保つために、平衡伝送線はできるだけ長くそのまま維持する。

図5 入力信号部のレイアウト(その2) 整合性を保つために、平衡伝送線はできるだけ長くそのまま維持する。 図6 評価系の構成

図6 評価系の構成