ガウシアンエッジの生成:Signal Integrity

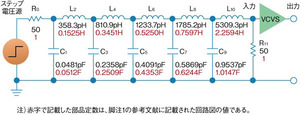

ステップ状に立ち上がる信号、降下する信号を図1に示すアナログフィルタ回路(5段のCLフィルタ回路)に通すと、その出力の立ち上がり/降下エッジは滑らかなガウス型エッジ(ガウシアンエッジ)となる。SPICEにより高速システムのシミュレーションを行う場合、このようなフィルタ回路によって信号エッジを生成すれば、折れ線(PWL:Piecewise-Linear)法を使用する場合に比べて、現実の信号の振る舞いをよりよく表現することができる。

図のアナログフィルタ回路は、パッシブフィルタの設計例を網羅したAnatol I Zverev氏の古典的著書『Handbook of Filter Synthesis』*1)から引用した。このハンドブックには、ガウシアンフィルタの近似法を含めて、さまざまなフィルタの回路構成がまとめられている。真のガウシアン応答は、無限時間前からスタートするとの仮定に基づくものなので、同氏が示したのはあくまでも近似法である。とはいえ、シミュレーションなどでの利用に、十分に堪えるものとなっている。その導出方法は、完全なガウシアンネットワーク関数の2乗をテイラー展開し、その10次までの項を使用したものだ。また、フィルタを構成する素子は、寄生要素を含まない理想素子であると仮定している。

Zverev氏の著書に記載されたフィルタ(以下、Zverev氏のフィルタ)は、フィルタの入力部に電流源を使用し、抵抗R0でシャントするという構造になっている。図1では、それとは異なり、電圧源と直列抵抗R0により入力部を構成している。いずれの方法でも、出力インピーダンスが50Ωのドライバを構成できる。電圧源を使用する場合、回路の出力での振幅は、電圧源の振幅のちょうど1/2とすることができる。

図1において黒字で記載している回路定数は、Zverev氏のフィルタの値とは異なる。同氏のフィルタは、図1で赤色の文字で記載した定数を使用しており、インピーダンスは1Ωとして設計されている。

一方、図1の黒字の定数は、インピーダンスが一般的な値である50Ωになるよう、筆者がスケーリングしたものだ。スケーリングは、Zverev氏のフィルタで使われている抵抗値とインダクタンスを50倍し、キャパシタンスを50で割ることで行っている。

Zverev氏のフィルタの特性は、カットオフ周波数(−3dB)が1rad/s、つまり0.159154Hzであり、10〜90%の立ち上がり/降下時間は2.12773sである。図1では、立ち上がり時間が100psとなるよう、キャパシタンスおよびインダクタンスのそれぞれを、元の値にτ/2.12773を乗じた値としている。ここでτは、目標とする立ち上がり時間であり、この例であれば100psである。抵抗値は、時間軸上でのスケーリングの計算に対しては変化しない。

このようにして計算した結果、インピーダンスが50Ωで、立ち上がり/降下時間が100psのフィルタが得られる。このフィルタの周波数特性は、−40dBまでは真のガウシアン応答に対し±1dBの範囲にあり、その後は60dB/octの傾斜で減衰する。このフィルタには10個の極があり、0〜50%の公称遅延量は10〜90%の立ち上がり時間の1.485倍となる。

Zverev氏のフィルタの出力には、バッファを使用することになる。SPICEの用語で言えば、理想的なバッファはVCVS(電圧制御電圧源)である。このバッファは、負荷を接続した場合にフィルタ特性が変化するのを防ぐ役割を果たす。シミュレーションでは、このバッファの出力に、信号源の出力抵抗とパッケージのモデルをつないで使用すればよい。

<筆者紹介>

Howard Johnson

Howard Johnson氏はSignal Consultingの学術博士。Oxford大学などで、デジタルエンジニアを対象にしたテクニカルワークショップを頻繁に開催している。ご意見は次のアドレスまで。www.sigcon.comまたはhowie03@sigcon.com。

脚注

※1…Zverev, Anatol I,"Handbook of Filter Synthesis", John Wiley & Sons, New York, 1967

Copyright © ITmedia, Inc. All Rights Reserved.