第9回 トランシーバを内蔵した低コストFPGAの活用法(前編):FPGA Insights

電子機器が市場で成功を収めるには、消費者が求める機能や性能を実現しつつ、適正な価格でタイムリーに製品化することが重要である。しかし、変わりやすい消費者のニーズを長期的に予測することは難しい。一方で、機器設計者には開発期間の短縮や製品コストの低減といったプレッシャーが強くなる。しかも、機器のパフォーマンスを高める新しいインターフェース技術や画像処理技術への迅速な対応も行わなければならない。最新のFPGAは設計者が直面するこうした課題に応えるための柔軟性を持ち合わせている。

半導体産業が好不況の波を繰り返しながらも、継続的な成長を遂げてきた背景には、微細加工技術の進展と応用市場の拡大がある。微細加工技術が1世代進むごとに同じチップサイズであれば、ほぼ2倍のトランジスタ数を集積でき、チップの高機能化を実現してきた。逆に同じトランジスタ数を集積するのであれば、チップ面積を約半分にすることができるため、チップコストの低減や高速動作を可能としてきた。その結果として、電子機器は主要な部品コストをさほど上げずに、高度な機能を少ないチップ数で実現することができ、複雑な演算を高速に実行することが可能となった。

しかし、微細化の進展などによって、新たな課題も浮かび上がってきた。それは世代交代ごとに膨れ上がるICチップの設計コストとICチップを量産するための設備投資費用である。ある会社のデータによると、ASIC/ASSP開発におけるプロセスノード(世代)ごとの設計コスト、マスクコストおよび量産立ち上げコストを合計すると、90nm世代では約21億円であったものが、45nm世代では約55億円となり、32nm世代では約90億円に達するとの見通しである。つまり、ASIC/ASSPを先端プロセスで新規に開発しても、携帯電話機や家庭用ゲーム機器のようなハイボリュームの製品向けでないと、事業としてはコスト割れが生じてしまうことになる。また、資金力に乏しい半導体ベンチャー企業などが優れたアイデアをICチップに落とし込もうとしても、最新のASIC/ASSPを使って事業化するモデルは、もはや成り立ちにくくなっている。

そこで注目を集めているのがFPGAを用いた回路設計である。FPGAはチップを設計する技術者が手元で回路を設計し、変更することができるプログラマブルなチップである。チップの設計が完了した後であっても機器の仕様変更や機能の追加などにも柔軟に対応することができる。また、FPGAであれば余分な在庫を抱える心配もない。しかも、新しいFPGAは最新のプロセス技術を用いて量産されるため、高い性能と低い消費電力を両立したチップを入手することができる。

これまで、ICチップの大量消費が期待される民生電子機器などの市場領域では主にASICやASSPが用いられ、消費するICチップの数量が比較的小規模で、仕様変更なども起こりうる可能性があるテレコム機器、半導体製造装置などの場合はFPGAが使われることが多かった。その間の中量規模を消費する市場領域では、過去は主流だったASIC/ASSPに加えてFPGAも用途に応じて使い分けされている。この中量規模の市場に対して、主なFPGAメーカーは「FPGAの新たな成長領域」と位置づけ、同市場にマッチする低コスト/低消費電力を実現したFPGAの製品強化を行っている。

システム全体のコストを低減

例えばFPGAの新たな成長領域に向けた製品の1つに、アルテラの「Cyclone IV」ファミリがある(写真1)。トランシーバを内蔵した「Cyclone IV GX」と、低消費電力化をさらに進めた「Cyclone IV E」の2種類の製品があり、ワイヤレス機器や放送機器、通信機器、民生電子機器、産業機器といった幅広い分野で使用できるという。

このようなFPGAをシステムアーキテクチャのキーコンポーネントとして用いることで、新製品開発に要する費用を削減しつつ、製品のライフサイクル全体を通じたTCO(Total Cost Ownership)の低減にもつながる。つまり、従来の機器設計に比べて、「より少ない人数」、「より少ない開発費」、「より少ない時間」で開発することが可能となるわけだ。それに加えて、既存製品をバージョンアップする際にも、単に使用する部品のコストを引き下げるのではなく、主要な回路ブロックを再設計し、新しい機能の追加と周辺回路をFPGA内に取り込むことで大幅なコスト削減効果が期待できる。

高速トランシーバを内蔵

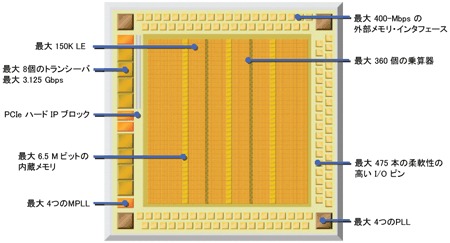

低コストのFPGAでありながら、高速トランシーバを内蔵するという新たな動きもある。この背景の1つには、デジタルテレビのフルHD化や3D表示への対応などがある。例えば、チューナ/ビデオ信号処理用基板とディスプレイパネル用基板を接続し、データ伝送するためのインターフェースの帯域幅が、従来のままだとボトルネックになる可能性がでてきているからだ。この課題を解決するためには、現行のLVDSのI/O数を増やすか、少ないI/O数で十分な帯域幅が得られる「V-by-One」など、新しいシリアルプロトコル規格を採用する方法がある。一般的に前者の場合、I/O数が増加することによって基板サイズが大きくなったり、消費電力の増加につながったりする。後者の場合は、外付けのチップが必要となったりすることがある。 「Cyclone IV GX」の場合は、低コスト製品でありながら通信速度が最大3.125ギガビット/秒(Gbps)のトランシーバを内蔵している。これによって、上述したI/O数や外付けチップの増加などの課題を解決しつつ、インターフェースの帯域幅のボトルネックを解消することができる。この高速トランシーバは、ギガビットイーサーネット(GbE)、PCI Express(PCIe)、CPRI(Common Public Radio Interface)、XAUI、3G トリプルレートSDI、Serial Rapid IO、SATA、DisplayPort、V-by-Oneなどのシリアルプロトコルをサポートしている。それに加え、PCIeはハードIPブロックとして用意されている(図1)。このため、FPGAのリソースも有効に活用することができるようになっている。

高速トランシーバを内蔵したFPGAは、すでにハイエンド品で用意されているが、主要なFPGAメーカーでは、低コスト製品でのシリーズ展開もこれから本格化するものと思われる。

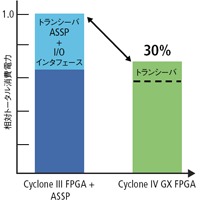

また、電子機器の設計において、機能や性能を高めつつコストや消費電力をさらに低減していくことは必須の要件である。これらを達成していくためには、ICチップ単体だけでなく回路ブロックとして設計を考慮する必要もある。例えば、従来のCyclone IIIファミリとトランシーバASSPを組み合わせた回路構成に比べて、Cyclone IV GXはトータルの消費電力を最大30%削減することが可能となった(図2)。これにより、熱対策用の部品を省くことができる。その上、FPGAに供給する電源電圧が2種類で済むため、従来のFPGAに比べて電源数の削減やプリント基板設計の簡素化、基板の小型化などを図ることができる。このことは、システム全体のコスト削減にもつながるというわけだ。

後編では、一例としてトランシーバを内蔵した低コスト/低消費電力の「Cyclone IV GX」を取り上げ、その特徴の1つである高速シリアル通信機能を活用した設計事例などを紹介する。

3月30日リリース!「Cyclone IV GX スタータ開発キット」

設計に必要なリソースをすべて同梱した、トランシーバ内蔵デバイス搭載の開発キット。PCI Express をハードIPでサポート。「今すぐ」「低コスト」「低消費電力」で設計・検証スタート可能。

公開中(2010年4月〜2010年12月掲載分)

第9回 トランシーバを内蔵した低コストFPGAの活用法(前編)

第10回 トランシーバを内蔵した低コストFPGAの活用法(後編)

第11回 FPGAの設計開発フロー:〜ステップ1 デザイン設計〜

第12回 FPGAの設計開発フロー:〜ステップ2 制約設定〜

第13回 FPGAの設計開発フロー:〜ステップ3 コンパイル〜

第14回 FPGAの設計開発フロー:〜ステップ4 プログラミング〜

第15回 DDR2 の実装からデバック手法:〜ステップ1 FPGA を用いた DDR2 SDRAMインタフェース〜

第16回 DDR2 の実装からデバッグ手法:〜ステップ2 DDR2 FPGA デザイン設計〜

第17回 DDR2 の実装からデバッグ手法:〜ステップ3 FPGA のデバッグ手法『SignalTap II Logic Analyzer』〜

第18回 DDR2 の実装からデバッグ手法:〜ステップ4 FPGA のデバッグ手法『Debug GUI』〜

第19回 FPGAで実現する 産業用ワイヤレスセンサーネットワーク(前編)

第20回 FPGAで実現する 産業用ワイヤレスセンサーネットワーク(後編)

第21回 産業機器におけるTCO ―FPGAで回路設計の発想を転換する(前編)

第22回 産業機器におけるTCO ―FPGAで回路設計の発想を転換する(後編)

第23回 低コストFPGAで実現するUSB3.0インタフェース 〜ステップ1:USB3.0の概要〜

第24回 低コストFPGAで実現するUSB3.0インタフェース 〜ステップ2:FPGAを用いたUSB3.0の基板設計〜

第25回 低コストFPGAで実現するUSB3.0インタフェース 〜ステップ3:USB3.0 Boardのベンチマーク測定〜

第26回 低コストFPGAで実現するUSB3.0インタフェース 〜ステップ4:USB3.0 Boardのリンク検証事例〜

関連情報

●業界最小コスト、最小消費電力FPGAによるトータル・システム・コストの削減

●Supporting Digital Television Trends with Next-Generation FPGAs[英文](和文は5月上旬リリース予定)

Copyright © ITmedia, Inc. All Rights Reserved.

提供:日本アルテラ株式会社

アイティメディア営業企画/制作:EDN Japan 編集部/掲載内容有効期限:2013年3月31日

FOR FPGA BEGINNERS [PR]

■FPGAとは

■無償ではじめるFPGA設計

FPGA LEARNING CENTER [PR]

FPGAについて、基礎からわかりやすく解説しています。

初級者から熟練者まで、FPGA設計技術を向上させたいすべての人のためのトレーニング講座。

オンライン講座は視聴無料です。