第14回 FPGA開発基礎:〜ステップ4 プログラミング〜:FPGA Insights

FPGAは、さまざまな電子機器の設計において「開発期間の短縮」や「コストダウン」といった、機器設計者が抱える悩みを解決できるデバイスの1つとして、注目を集めている。本連載では、「これから本格的にFPGAを使いこなしたい」という設計者向けに『これさえ知っていればFPGAの設計ができる』という4つの基本ステップを4回にわたって解説している。これまでステップ1で「デザイン(論理回路)設計」について、ステップ2で「制約設定」について、ステップ3では「コンパイル」について、それぞれ述べてきた。今回は最後のステップとなる『プログラミング』についてわかりやすく解説する。

前回のステップ3では、設計した論理回路を具体的なゲート回路に変換する「コンパイル」について紹介した。「コンパイル」が完了したら、コンパイルしたデータをデバイスに書き込む前に、TimeQuestを用いてスタティック・タイミング解析を実施する。また、TimeQuestで与えきれていない制約 (非同期回路部分など) があった場合は、タイミング・シミュレーションを実施することで、タイミング・エラーの有無などを確認することが出来る。これらは、回路データを実際のデバイスに書き込んだときに、配置配線などで生じる遅延によって、動作等に問題が発生しないかどうかを事前に確認するための作業となる。

タイミング・シミュレーションによる検証を実施する場合のツールとしては、メンターグラフィックスの「ModelSim-Altera Starter Edition」(無償)や「ModelSim-Altera Edition」(有償)などがある。これらのソフトウエアは、Quartus IIと一緒にアルテラのウェブサイトからダウンロードすることができる。

こうしたスタティック・タイミング解析、タイミング・シミュレーションによって、設計者の要求どおりに回路が正しく動作することが分かったら、次のステップでは回路データを実際のデバイスへプログラミング (デバイスへの書き込み) することになる。

「Start」ボタンで書き込み実行

ステップ4 プログラミング

ステップ1〜ステップ3で紹介した「デザイン」、「制約設定」、「コンパイル」と同様、デバイスへの書き込みもGUI で作業することができる。

実際に回路データをデバイスへ書き込むときには、プログラミング・ハードウエアを使用する。例えば、Quartus II がインストールされたパソコンから、デバイスを実装した基板に回路データをダウンロードする場合に用いる接続ケーブルとして、アルテラではUSB通信タイプの「USB-BlasterTM」やパラレルポート通信タイプの「ByteBlasterTM II」、イーサネット RJ-45 タイプの「EthernetBlaster」などを用意している。これらのケーブルはアルテラの代理店あるいはオンラインショップで購入できる。これらのケーブルをはじめて使用する場合は、事前に各プログラミング・ハードウエア用のドライバをパソコンへインストールしておく必要がある。

デバイスへのデータ書き込みには、「Quartus II がインストールされたパソコン」、「アルテラ製のダウンロード・ケーブル」および「デバイスが実装された基板」の 3 点がそろっていれば、その場で書き込み作業が行える。ダウンロード・ケーブルは、アルテラ製のデバイスであれば、搭載するデバイスの種類に関係なく使用することができる。このため、デザインやデバイスを変更しても、従来のケーブルを流用することができ、その都度ケーブルを買い替えるなどの新たな費用が発生することはない。

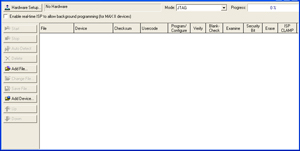

ここまでは、使用するツール環境について述べてきた。ここからは実際にこれらのツールを使って、どの様に書き込み作業を行っていくかを簡単に説明する。デバイスへの書き込みは、設計ツールの 「Programmer 」と呼ばれる機能を使用する。Programmer を起動すると画面上には図1のようなGUI が表示される。

Programmer の画面上から、書き込みに関するさまざまな設定を行うことができる。その中から代表的な設定項目をいくつか紹介する。

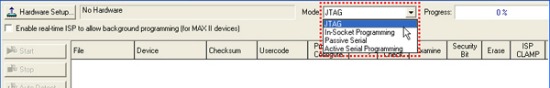

プログラミング・モードの選択

デバイスへの書き込みを実行する場合、FPGAを実装したプリント基板の構成などによってプログラミングの方式が異なるので注意しなければならない。まずはFPGAが実装されたプリント基板の構成に適したモードをプルダウンメニューより選択する必要がある(図2)。Quartus IIでは、オンボードで書き込む方法として3つのモードが用意されている。例えば、JTAGピンを使って直接FPGAに書き込む場合は「JPEGモード」を選ぶ。また、コンフィギュレーション・デバイスとしてEPCを使っている場合は「Passive Serialモード」を、アルテラのコンフィギュレーション ROM であるEPCSを使っている場合には「Active Serial Programming モード」を、それぞれ選択することになる。また、オフボードでの書き込みには「In-Socket Programmingモード」で対応しているが、書き込み時に専用のライター(PL-APU)を用意する必要がある。

プログラミング・ハードウエアの設定

プログラミング・モードの選択が完了したら、次は本稿の前半で述べたプログラミング・ハードウエア(ダウンロード・ケーブル)を選ぶ。実際に使用するハードウエアの種類(USB通信タイプ、パラレルポート通信タイプ、イーサネット RJ-45 タイプ)の設定を画面上のGUIで行う。

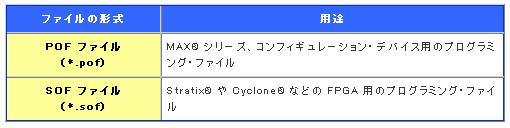

プログラミング・ファイルの選択

プログラミング・ハードウエアを設定した後は、デバイスへ書き込むプログラミング・ファイルを選択する。ファイルの形式としては、主に表1に示したような種類がある。ここでは書き込みを行うターゲット・デバイスや、用途にあわせて適切なファイルを選択することになる。

プログラミング・オプションの選択

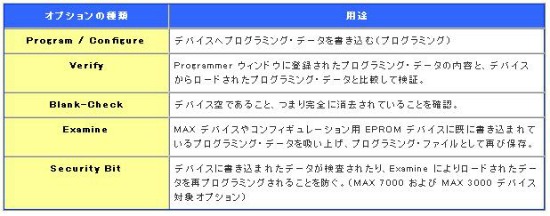

Programmer では、図3のような通常の書き込み以外の操作を、チェックボックスにチェックマークを付けるだけで実行できる。オプションの種類とその用途については図4に示す。以上でプログラミングに必要な設定が完了する。

これからは、実際のデバイスへ回路データを書き込むための作業に入る。書き込みの開始は、Programmer ウィンドウの「 Start 」ボタンを押すだけの簡単操作である(図5)。この画面上にはファイル名やデバイス名が表示され、設定内容などを確認することができる。また、画面右肩には書き込み作業の進捗状況がパーセントで表示される。この数値が100%になれば書き込みが完了したことになる。以上で、プログラミングの作業は終了する。

ロジックアナライザ機能を標準搭載

◆デバック手法

これまで説明を行ってきた 「デザイン作成〜制約設定〜プログラミング」の作業 に加えて、プログラミング後に、デバック作業も行うことができる。ここでいうデバッグ作業とは、回路データを実チップに書き込んだ後で、FPGA の動作に不具合があった場合、FPGA の出力ピンの信号や、FPGA 内部の信号を観測し、検証を行う作業のことを指す。

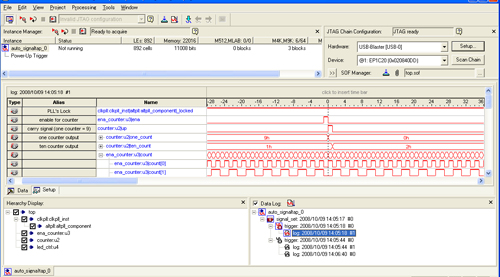

Quartus II では、いくつかのデバック手法が用意されている。今回はその中から、「SignalTap II 」の機能を紹介する。これは、Quartus II に標準搭載されたロジックアナライザの機能である。この機能により、別途外部に測定器を用意することなく、内部動作の確認を行うことができる(図6)。

この機能がないと、FPGAをデバッグするために、モニターピン用の空きピンが別途必要となったり、デザイン(論理回路)を書き直ししたり、基板上にあらかじめデバッグ用の配線を用意したりしておかなければならなかった。このような対応は設計者を悩ませる要因の1つとなっていた。

これに対してSignalTap II は、プログラミングを実行する前に、用意された専用の画面上から、観測したい FPGA 内部の中間信号を指定するだけで、デバッグを行うための準備は終わる。これだけで、デバッグ用の回路を作ることができ、デザインの記述を変更したりする必要は一切ない。このデバッグ用回路と設計者の回路データを一緒に、FPGA へプログラミングすることになる。

デバッグが必要な時には、USB-Blaster等のダウンロード・ケーブルを使用する。デバッグが実行されると、Quartus II は観測したい内部信号をモニターし、画面上にその波形を表示させることができる。内部信号のデータ取得はJTAG ピンを利用して行われるため、ユーザー I/O ピンは一切必要がない。つまり、JTAG の配線さえしておけば、デバッグのためにプリント基板の配線を変更したりする必要はなく、チェックしたい内部信号のタイミング検証が手軽に行えるというわけだ。なお、「デバッグ手法」については、本連載の後半で改めてテーマを設け、より詳細に解説する予定である。

以上でFPGA設計の基本的なフローは完了である。これまで、4回にわたってFPGAの設計開発フローの中で、「これさえ知っていればFPGAの設計ができる」という4つの基本ステップを取り上げ、一歩ずつ解説してきた。これまでFPGAになじみの薄かった方にも思っていたほどには難しくない、と感じていただけただろうか。 次回からはより実践的な「ボードを使った回路設計」についてわかりやすく解説する。

公開中(2010年4月〜2010年12月掲載分)

第9回 トランシーバを内蔵した低コストFPGAの活用法(前編)

第10回 トランシーバを内蔵した低コストFPGAの活用法(後編)

第15回 DDR2 の実装からデバック手法:〜ステップ1 FPGA を用いた DDR2 SDRAMインタフェース〜

第16回 DDR2 の実装からデバッグ手法:〜ステップ2 DDR2 FPGA デザイン設計〜

第17回 DDR2 の実装からデバッグ手法:〜ステップ3 FPGA のデバッグ手法『SignalTap II Logic Analyzer』〜

第18回 DDR2 の実装からデバッグ手法:〜ステップ4 FPGA のデバッグ手法『Debug GUI』〜

第19回 FPGAで実現する 産業用ワイヤレスセンサーネットワーク(前編)

第20回 FPGAで実現する 産業用ワイヤレスセンサーネットワーク(後編)

第21回 産業機器におけるTCO ―FPGAで回路設計の発想を転換する(前編)

第22回 産業機器におけるTCO ―FPGAで回路設計の発想を転換する(後編)

第23回 低コストFPGAで実現するUSB3.0インタフェース 〜ステップ1:USB3.0の概要〜

第24回 低コストFPGAで実現するUSB3.0インタフェース 〜ステップ2:FPGAを用いたUSB3.0の基板設計〜

第25回 低コストFPGAで実現するUSB3.0インタフェース 〜ステップ3:USB3.0 Boardのベンチマーク測定〜

第26回 低コストFPGAで実現するUSB3.0インタフェース 〜ステップ4:USB3.0 Boardのリンク検証事例〜

関連情報

初めてFPGA開発ソフトウェアを使う方を対象に、「Quartus® II」を使用した基本的なデザイン・フローを、デモ形式で解説。

●USB-Blasterダウンロード・ケーブル・ユーザガイド

●SignalTap II エンベデッド・ロジック・アナライザを使用したデザインのデバッグ

Copyright © ITmedia, Inc. All Rights Reserved.

提供:日本アルテラ株式会社

アイティメディア営業企画/制作:EDN Japan 編集部/掲載内容有効期限:2013年3月31日

FOR FPGA BEGINNERS [PR]

■FPGAとは

■無償ではじめるFPGA設計

FPGA LEARNING CENTER [PR]

FPGAについて、基礎からわかりやすく解説しています。

初級者から熟練者まで、FPGA設計技術を向上させたいすべての人のためのトレーニング講座。

オンライン講座は視聴無料です。

表1:プログラミング・ファイルの形式とその主な用途

表1:プログラミング・ファイルの形式とその主な用途 図4:プログラミング・オプションの種類とその用途

図4:プログラミング・オプションの種類とその用途