第26回 低コストFPGAで実現するUSB3.0インタフェース 〜ステップ4:USB3.0 Boardのリンク検証事例〜:FPGA Insights

本連載では、USB3.0インタフェースを比較的容易に、短期間で実現できる手法の1つとして、アルテラの低コストFPGA「Cyclone III」を用いたUSB3.0ソリューションについて分かりやすく紹介してきた。ステップ4では、そのソリューションの核となるアルティマ製の「Cyclone III USB3.0 Board」と、市販されているホストボードおよびマザーボードを使って接続確認を行うとともに、その実例に基づいて接続不具合が生じた際の検証項目や原因解明の手法などについて解説する。

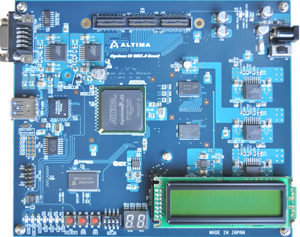

アルティマは、Cyclone III USB3.0 Board(写真1)と、市販されている2社のUSB3.0ホストボードおよび3社のマザーボードをそれぞれ組み合わせて、リンクの検証を行った。リンクの検証にはEllisys社製のプロトコルアナライザ「EX280」、Tektronix社製のロジックアナライザ「TLA5203B」、同ストレージオシロスコープ「DAS72004」などを使った。いくつかの組み合わせでUSB3.0インタフェースの接続試験を行ったところ、このうち1社のマザーボードを使った時に、ホスト側とリンクできない現象が生じた。

この原因を探るため、アルティマは「電源の検証」や「ホスト側とマザーボードとのリンク検証」、ロジックアナライザによるFPGAとPHYチップ側の「PIPE IIIの検証」、プロトコルアナライザによるPHYチップとホストボード間の「USB3.0ラインの検証」、およびストレージオシロスコープによる「USB3.0コンプライアンスの検証」(マザーボードから供給されるPCIe用リファレンス・クロック)などを試みた。

検証作業ではまず、電源に注目して、電源ケーブルやアドインコネクタに関する電源の適合性を検証した。その結果、PCIe(3.3V±9%)、SATA電源コネクタ(5.0V±8%)、SATA電源コネクタとPCIe(12V±8%)のいずれの電圧にも問題はないことがわかった。

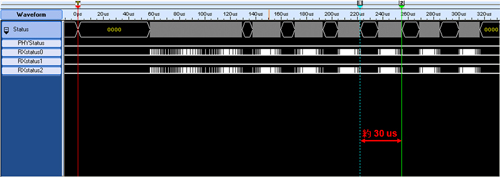

次に、Cyclone III USB3.0 Boardやホストボードを接続して、マザーボードとのリンク検証を行った。この結果、3社のマザーボードのうち1社の製品のみがリンクすることができなかった。さらに、2組のシステムについてFPGAとPHYチップ間の動作を確認するため、PIPE III 信号をロジックアナライザで検証した。その結果、図1に示す通り、リンクすることができなかったマザーボードを使用したシステムについては、PIPE IIIの信号「RX_STATUS」でエラーが検出された(デバイス側)。測定したデータから30μs周期でエラーと正常動作を繰り返していることが分かった。その原因としてローカルクロック(送信側)がリカバリクロック(受信側)より速い周波数で動作している可能性が高いと推定される。

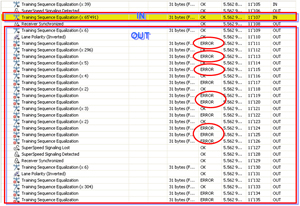

続いて、プロトコルアナライザを用いて、Cyclone III USB3.0 Boardやホストボード、マザーボードを接続した状態で、USB3.0 ラインの通信状況をプロトコル単位で確認した。リンクできなかったマザーボードは、トレーニングシーケンス(TSEQ)でIN(ホストのRX)信号は正常に動作していたものの、OUT(ホストのTX)信号にエラーが多発し、連続してデータが送られていないことが判明した(図2)。

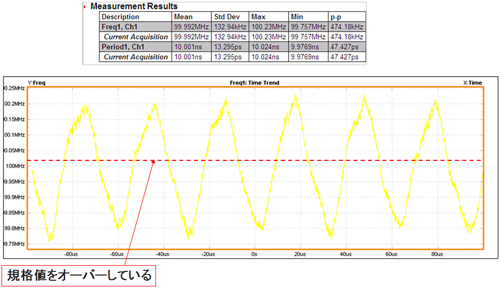

PCIe用リファレンス・クロックが原因

この原因を追究するため、ストレージオシロスコープを使って、リンクできなかったマザーボードと正常なホストボードを接続した状態でUSB3.0インタフェースのSSモードでのOUT信号を測定してみた。そうしたところ、PCIe規格で定められているリファレンス・クロック(100MHz+300〜−5300ppm)を超える規格外の信号が出力されていた。これが原因でリンクできないことが分かった(図3)。なお、ここで「Fail or Pass」判定を行った値は「Universal Serial Bus3.0 Specification Rev1.0」に記載されている数値を参考にした。

以上のような測定結果から、Cyclone III USB3.0 Boardとホスト(PC)側リンクが安定しない原因として、ホスト側から送信される信号が、USB3.0インタフェース規格に準拠していない可能性が考えられる。つまり、ホストボードに搭載されているUSB3.0 to PCIeブリッジチップが、マザーボードから供給されるPCIe用リファレンス・クロックに追従して、USB3.0インタフェース用のリファレンス・クロックを生成している可能性が高い。したがって、マザーボードより供給されるPCIe用リファレンス・クロックがPCIeの規格に準拠していることが必要である。

本連載では低コストFPGAを有効活用してもらうために、USB3.0インタフェースへの応用を紹介してきた。USBインタフェースは、もともとパソコンと周辺機器を接続するインタフェースとして広く普及してきた。次世代インタフェースとして注目されているUSB3.0は、伝送速度が高速で高精細な動画像の伝送にも適していることから、その用途はさらに拡大すると見られている。

一方で、USB3.0に対応するASSP/ASICの開発は機器設計者にとって大きな負担となっている。USB3.0インタフェースを実現する手段はいくつかある。その1つとして、低コストのFPGAとPHYチップを組み合わせ、サードパーティのハードウエア/ソフトウエアIPを活用する方法がある。開発リスクを抑えられ、開発期間も短縮することが可能なこのUSB3.0ソリューションを、積極的に活用してみる価値は十分にありそうだ。

公開中(2010年4月〜2010年12月掲載分)

第9回 トランシーバを内蔵した低コストFPGAの活用法(前編)

第10回 トランシーバを内蔵した低コストFPGAの活用法(後編)

第11回 FPGAの設計開発フロー:〜ステップ1 デザイン設計〜

第12回 FPGAの設計開発フロー:〜ステップ2 制約設定〜

第13回 FPGAの設計開発フロー:〜ステップ3 コンパイル〜

第14回 FPGAの設計開発フロー:〜ステップ4 プログラミング〜

第15回 DDR2 の実装からデバック手法:〜ステップ1 FPGA を用いた DDR2 SDRAMインタフェース〜

第16回 DDR2 の実装からデバッグ手法:〜ステップ2 DDR2 FPGA デザイン設計〜

第17回 DDR2 の実装からデバッグ手法:〜ステップ3 FPGA のデバッグ手法『SignalTap II Logic Analyzer』〜

第18回 DDR2 の実装からデバッグ手法:〜ステップ4 FPGA のデバッグ手法『Debug GUI』〜

第19回 FPGAで実現する 産業用ワイヤレスセンサーネットワーク(前編)

第20回 FPGAで実現する 産業用ワイヤレスセンサーネットワーク(後編)

第21回 産業機器におけるTCO ―FPGAで回路設計の発想を転換する(前編)

第22回 産業機器におけるTCO ―FPGAで回路設計の発想を転換する(後編)

第23回 低コストFPGAで実現するUSB3.0インタフェース 〜ステップ1:USB3.0の概要〜

第24回 低コストFPGAで実現するUSB3.0インタフェース 〜ステップ2:FPGAを用いたUSB3.0の基板設計〜

第25回 低コストFPGAで実現するUSB3.0インタフェース 〜ステップ3:USB3.0 Boardのベンチマーク測定〜

第26回 低コストFPGAで実現するUSB3.0インタフェース 〜ステップ4:USB3.0 Boardのリンク検証事例〜

関連情報

●アルティマ、国内初*「低コストFPGAで実現するUSB3.0ソリューション」を発表[プレスリリース]

Copyright © ITmedia, Inc. All Rights Reserved.

提供:日本アルテラ株式会社

アイティメディア営業企画/制作:EDN Japan 編集部/掲載内容有効期限:2013年3月31日

FOR FPGA BEGINNERS [PR]

■FPGAとは

■無償ではじめるFPGA設計

FPGA LEARNING CENTER [PR]

FPGAについて、基礎からわかりやすく解説しています。

初級者から熟練者まで、FPGA設計技術を向上させたいすべての人のためのトレーニング講座。

オンライン講座は視聴無料です。