第13回 FPGA開発基礎:〜ステップ3 コンパイル〜:FPGA Insights

FPGAは、さまざまな電子機器の設計において「開発期間の短縮」や「コストダウン」といった、機器設計者が抱える悩みを解決できるデバイスの1つとして、注目を集めている。本連載では、「これから本格的にFPGAを使いこなしたい」という設計者向けに『これさえ知っていればFPGAの設計ができる』という4つの基本ステップを4回にわたって解説している。 これまでステップ1で「デザイン(論理回路)設計」について、ステップ2で「制約設定」についてそれぞれわかりやすく述べてきた。今回はステップ3となる『コンパイル』について解説する。

アイコンをクリックするだけでコンパイルを実行

ステップ3:コンパイル

デザイン作成が終了し、各種制約の設定を行った後、「コンパイル」を実行する。アルテラ社の開発ソフトウェア「Quartus II」では、画面上のアイコンをクリックするだけでこれら一連の作業が始まり、そのあとは自動的に実行される。このため、設計者の手をわずらわせることはない。

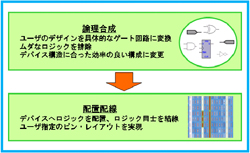

コンパイルとは、「論理合成」と「配置配線」を行う作業のことをさす。「論理合成」とは、設計者がハードウエア記述言語や回路図で作成したデザイン(論理回路)を、「 AND 」や「フリップフロップ」などの具体的なゲート回路に変換する作業のことである。

論理合成が完了すると、使用するFPGA の構造に合わせて、ロジックやピンの配置を決め、ロジック同士やロジックとピン間の配線を自動で行う。これを「配置配線」と呼ぶ(図1)。

コンパイラは、論理合成や配置配線の機能以外にも回路図の接続チェックや言語の構文チェック、プログラミング用ファイルの生成、タイミング検証などの機能を備えている。

ここからは、コンパイル作業の具体的な実行方法を解説する。Quartus IIを用いると、図2に示した赤丸で囲われた画面上のアイコンをクリックするだけで、前述した論理合成から配置配線、回路図の接続チェック、プログラミング用ファイルの生成といった作業が、ツール上で自動的に行われる。その上、ハードウエア記述言語や回路図で作成したデザイン(論理回路)を、無駄なロジックを省き、効率の良いゲート回路に変換する。さらに使用する FPGA の内部構造を考慮しつつ、実装効率の高い構成となるように、乗算器やメモリーブロックの最適化も、開発ソフトウェアが同時に自動で実行するのだ。このように、Quartus II ではコンパイルをはじめとして、さまざまな機能を実行する場合に、画面上にあるアイコンをクリックするだけの簡単操作で行えるのが大きな特徴の1つだ。

コンパイルが終了すると、各種コンパイル結果が生成される。結果の確認も、もちろん GUI で行うことができる。以下に代表的ないくつかの例を紹介する。

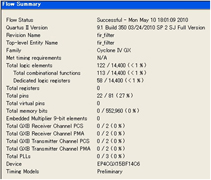

まずは "Flow Summary" である(図3)。ここには、デバイス全体のリソース情報のサマリーが表示されている。ここではデバイス、ロジック・エレメント/メモリーブロック/DSP ブロック/PLL などの使用率を確認することができる。

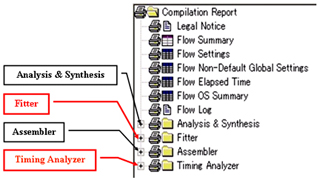

詳細な内容が確認できる項目に関しては、図4のように表示される。確認したい項目をダブルクリックすると、Summaryよりも詳細なレポートを表示させることができる。「Analysis & Synthesis」 は論理合成された結果についてのレポート、「Fitter」 はデバイスに配置配線された結果のレポート、「Assembler」 はプログラミング・ファイルに関するレポート、「Timing Analyzer」 はタイミング解析した結果のサマリー・レポートである。設計者には、最低限でも同期設計で重要となる「Fitter」 と「Timing Analyzer」 の項目については必ずチェックしてもらいたい。

コンパイル時間を最大70%短縮

ここからは、Quartus II に搭載されている、便利なコンパイル手法「インクリメンタル・コンパイル」について、その概要を紹介していく。

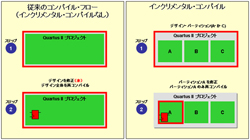

従来の一般的なコンパイル手法では、デザインに変更が生じた時には、それが局所的(ある機能ブロックなどだけ)であっても、図5の左側のようにデザイン全体を再度コンパイルする必要があった。全体のコンパイルを繰り返し行うために、その結果としてコンパイル時間が予定より大幅に増加したり、タイミングがミートしなくなってしまったりするといった問題が生じることがある。

これに対して、Quartus II のインクリメンタル・コンパイル手法を用いると、図5の右側のように、チップ全体を機能モジュール単位など、任意にグループ(パーティション)分けをして、個別にコンパイルすることもできる。このため、チップ全体のコンパイルが完了したあとで、局所的にデザインを変更する場合でも、Quartus II はデザインを処理するときに設計者が割り当てたパーティション(図のA、B、Cに相当)に従う。

この機能によって、設計者は特定のパーティション(変更が生じた機能ブロックのみ、この図ではA)を最適化させながら、デザイン変更がないそれ以外のパーティション(この図ではB、C)は、その前に実行したコンパイルの結果をそのまま維持することができる。特定のデザイン・パーティションには高度な最適化技術を適用し、それ以外のパーティションは何も変更を加えず、性能を維持することによって、タイミング・クロージャの向上を図ることが可能となる。

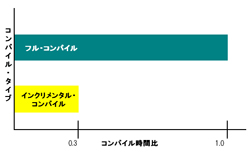

インクリメンタル・コンパイル手法を用いると、デザインで変更されていないパーティションのコンパイル結果と性能は維持しつつ、変更されたデザインが含まれるパーティションのみ、再コンパイルさせることによって、デザイン変更に伴うコンパイルの繰り返し時間を最大70%と大幅に短縮させることが可能となる(図6)。

例えば、デザイン変更時に常にフル・コンパイルをする手法では1 日あたり1〜2 回しか実行できなかったデザインの繰り返し作業が、インクリメンタル・コンパイルの手法を用いることによって 4〜10 回も実行することが可能となる。このことは、設計者の生産性を大幅に向上させ、設計期間やコストの削減にもつながるため、タイムリーな製品開発を強く求められているアプリケーション向けFPGAの設計には特に有効な手法といえよう。

次回のステップ4では、コンパイルが完了した回路データを、実際のFPGAに書き込む「プログラミング」について、わかりやすく解説する。

公開中(2010年4月〜2010年12月掲載分)

第9回 トランシーバを内蔵した低コストFPGAの活用法(前編)

第10回 トランシーバを内蔵した低コストFPGAの活用法(後編)

第11回 FPGAの設計開発フロー:〜ステップ1 デザイン設計〜

第12回 FPGAの設計開発フロー:〜ステップ2 制約設定〜

第13回 FPGAの設計開発フロー:〜ステップ3 コンパイル〜

第14回 FPGAの設計開発フロー:〜ステップ4 プログラミング〜

第15回 DDR2 の実装からデバック手法:〜ステップ1 FPGA を用いた DDR2 SDRAMインタフェース〜

第16回 DDR2 の実装からデバッグ手法:〜ステップ2 DDR2 FPGA デザイン設計〜

第17回 DDR2 の実装からデバッグ手法:〜ステップ3 FPGA のデバッグ手法『SignalTap II Logic Analyzer』〜

第18回 DDR2 の実装からデバッグ手法:〜ステップ4 FPGA のデバッグ手法『Debug GUI』〜

第19回 FPGAで実現する 産業用ワイヤレスセンサーネットワーク(前編)

第20回 FPGAで実現する 産業用ワイヤレスセンサーネットワーク(後編)

第21回 産業機器におけるTCO ―FPGAで回路設計の発想を転換する(前編)

第22回 産業機器におけるTCO ―FPGAで回路設計の発想を転換する(後編)

第23回 低コストFPGAで実現するUSB3.0インタフェース 〜ステップ1:USB3.0の概要〜

第24回 低コストFPGAで実現するUSB3.0インタフェース 〜ステップ2:FPGAを用いたUSB3.0の基板設計〜

第25回 低コストFPGAで実現するUSB3.0インタフェース 〜ステップ3:USB3.0 Boardのベンチマーク測定〜

第26回 低コストFPGAで実現するUSB3.0インタフェース 〜ステップ4:USB3.0 Boardのリンク検証事例〜

関連情報

●Quartus II インクリメンタル・コンパイルによる生産性の向上

初めてFPGA開発ソフトウェアを使う方を対象に、「Quartus® II」を使用した基本的なデザイン・フローを、デモ形式で解説。

Copyright © ITmedia, Inc. All Rights Reserved.

提供:日本アルテラ株式会社

アイティメディア営業企画/制作:EDN Japan 編集部/掲載内容有効期限:2013年3月31日

FOR FPGA BEGINNERS [PR]

■FPGAとは

■無償ではじめるFPGA設計

FPGA LEARNING CENTER [PR]

FPGAについて、基礎からわかりやすく解説しています。

初級者から熟練者まで、FPGA設計技術を向上させたいすべての人のためのトレーニング講座。

オンライン講座は視聴無料です。