第11回 技術者のための回路設計開発フロー その1「デザイン設計編」:FPGA Insights

FPGAの用途が民生電子機器や産業機器などにも拡大している。「開発期間の短縮」や「コストダウン」といった、機器設計者が抱える悩みを解決できる手段の1つとして、FPGAの認知度が高まってきたからだ。合わせて、開発ツールも高機能/高性能化しつつ、GUIの採用などで操作性が格段に進化していることもその理由として挙げることができよう。これまでFPGAになじみの薄かった設計者にとっても、さまざまな電子機器の設計にFPGAを使いこなしてみる好機である。まずは『これさえ知っていればFPGAの設計ができる』という4つの基本ステップを4回にわたって解説する。

本連載では、これまでFPGA設計を行ったことがない技術者であっても、すぐにFPGAを製品開発に利用することができるよう、その設計開発フローと開発工程の概要をわかりやすく紹介する。

FPGA を設計するためのフローは、図1のように仕様書の作成からネットリストの出力まで、いくつかのステップに分類される。ASIC設計においてもほぼ同様のフローとなるので、ASIC設計者にも馴染みがあるのではないだろうか。ASIC設計では、サードベンダー各社から提供されるさまざまな設計ツールを組み合わせて使用することが多く、ASICを設計する技術者が、各ツールの機能や作業手順を覚えたり、データベースの共有化を図ったりする必要もある。しかし、FPGA設計ではデザインの作成からネットリストの出力まで、全てのステップに対応することができる設計ツールが用意されているため、複数のツールの操作を覚えなくて済む。

ステップ1:デザインの設計

「1つの設計ツールですべての設計工程に対応」

FPGAやASICを設計する際、まずそのチップでどのような機能を実現するのかを定義する仕様書を作成する。設計者は確定したその仕様書に基づいて、論理回路の設計を行い、実際のチップに落とし込んでいく。ここでは、FPGA設計ツールの一例として、アルテラの統合開発ソフトウェア「Quartus® II 」を使ったFPGAの設計フローを紹介する。Quartus II は、FPGA/CPLDの回路設計から論理合成、配置配線、タイミング検証、デバイスへのプログラミングおよびそのあとのデバッグまで、一貫して行うことができる開発ツールである。しかも、Quartus II は各ステップの開発作業を、より簡単に行えるようにユーザーインターフェースなどが工夫されている。

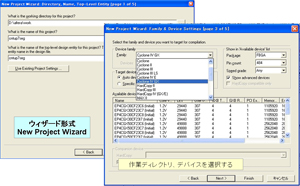

「ウィザード形式で簡単に設定」

プロジェクトの作成

FPGAやASICの設計者は、設計に着手する前に、回路設計の工程をプロジェクト単位で管理するのが一般的である。ASICの場合は、人、FPGAの場合は、ツールによる管理となる。

Quartus II は、プロジェクト作成の作業をウィザード形式で簡単に進めることができるのが大きな特徴の1つである(図2)。これによって、作業ディレクトリの指定やデザインファイルの登録、使用するデバイスファミリの選択、 EDA ツールの指定など、設計に必要な基本情報を、パソコンの画面上から簡単に設定することができる。

例えば、作業ディレクトリの指定では、プロジェクト名やデザインファイル名をつけたフォルダを作成する。すでに開発済みのデザインファイルがある場合には、そのファイルを登録することができる。使用するデバイスの選択も比較的簡単に行える。Quartus II にはアルテラが供給するFPGA/CPLDの製品群がリストアップされており、その中からファミリ名や製品型番を選択すれば登録される仕組みだ。具体的な製品型番がわからなくても、フィルター機能を使えば、「パッケージ」や「ピンカウント」、「スピードグレード」を指定するだけで、ツール側でフィルターされ、目的のデバイスを見つけ易くすることができる。設計開始時点で使用するデバイスが確定していない場合には「オートデバイス」を選択しておけば、ツール側で最適なデバイスを選択してくれる。プロジェクト作成の工程では、最低でもプロジェクトの概要と使用するチップの選択だけ行い、その内容を確認してフィニッシュボタンをクリックすれば、プロジェクト作成は完了する。

「設計の柔軟性を高め、簡便な操作性を実現する入力手法」

デザインの作成

プロジェクトの作成が終わると、デザイン(論理回路)の作成に移る。ASICの論理回路設計では、一般的にハードウエア記述言語を用いて設計が行われる。Quartus IIでは、代表的な手法であるハードウエア記述言語の「VHDL 入力」、「Verilog HDL 入力」に加えて、「回路図入力」などのデザイン入力手法にも対応している(図3)。各入力手法にはそれぞれ特徴があり、回路図入力ではデザインの視認性の良さと接続性の容易さを実現している。回路規模が比較的小さいTTLなどの設計では、回路図入力に慣れ親しんでいる設計者も多く、ハードウエア記述言語を新たに理解することなく、FPGAの回路設計を行うことができる。また、言語入力では文法に従い文字を色分けで表示する便利なエディタで設計が行えるなど、通常のテキスト・エディタには無い工夫が施されている。

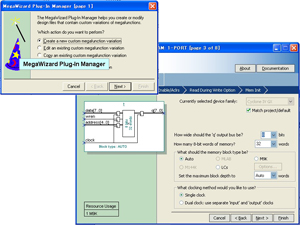

これ以外にも、Quartus II は便利なデザイン入力手法として「MegaWizard Plug-In Manager」機能を備えている(図4)。この機能を活用すれば、あらかじめ用意されたデザイン・ブロックである「アルテラ・メガファンクション」のパラメータを変更するだけで、メガファンクションをカスタマイズした複雑な回路でも、簡単な操作のみで作成することができる。作成したデザインは言語形式のライブラリでもシンボル・ブロックでも生成することができる。このため、言語設計者と回路図設計者の双方が容易に出力データを利用することができる。

さらに、MegaWizard Plug-In Manager機能を活用することで、以下のような設計上の利点が得られる。

- GUI でパラメータを変更するだけの簡単な操作性と設計の柔軟性

- デザイン作成の時間が短縮でき、ユーザー・デザインへの接続が容易

- アルテラ製デバイスに最適なロジック構成

- セル使用量の節約やパフォーマンスの向上

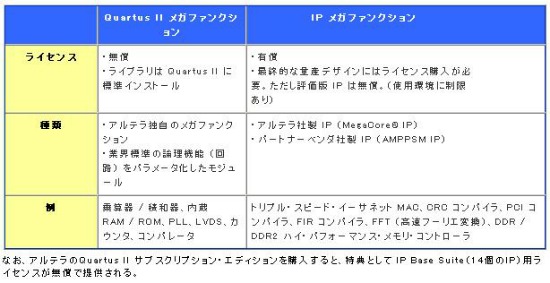

また、アルテラのFPGAにはメガファンクションとして「Quartus II メガファンクション」と、「IPメガファンクション」の2種類が用意されている。それぞれの特徴を表1に示す。

上述したデザイン入力方法に基づいてFPGAの論理回路設計を行えば、設計者が期待する設計仕様を容易に実現していくことが可能となる。論理回路の設計が完了したあとに、その回路が期待した動作をするかどうかを確認するために 「ファンクション・シミュレーション」 を行う。もし、期待値通りの動作にならなければ、記述を修正したりバグを取り除いたりする作業を行って設計が完了する。

次回の「ステップ2」では、FPGAを設計するに当たっての制約設定に関して、設計ツールが備えている代表的な機能について、その概要を述べる。

公開中(2010年4月〜2010年12月掲載分)

第9回 トランシーバを内蔵した低コストFPGAの活用法(前編)

第10回 トランシーバを内蔵した低コストFPGAの活用法(後編)

第11回 FPGAの設計開発フロー:〜ステップ1 デザイン設計〜

第12回 FPGAの設計開発フロー:〜ステップ2 制約設定〜

第13回 FPGAの設計開発フロー:〜ステップ3 コンパイル〜

第14回 FPGAの設計開発フロー:〜ステップ4 プログラミング〜

第15回 DDR2 の実装からデバック手法:〜ステップ1 FPGA を用いた DDR2 SDRAMインタフェース〜

第16回 DDR2 の実装からデバッグ手法:〜ステップ2 DDR2 FPGA デザイン設計〜

第17回 DDR2 の実装からデバッグ手法:〜ステップ3 FPGA のデバッグ手法『SignalTap II Logic Analyzer』〜

第18回 DDR2 の実装からデバッグ手法:〜ステップ4 FPGA のデバッグ手法『Debug GUI』〜

第19回 FPGAで実現する 産業用ワイヤレスセンサーネットワーク(前編)

第20回 FPGAで実現する 産業用ワイヤレスセンサーネットワーク(後編)

第21回 産業機器におけるTCO ―FPGAで回路設計の発想を転換する(前編)

第22回 産業機器におけるTCO ―FPGAで回路設計の発想を転換する(後編)

第23回 低コストFPGAで実現するUSB3.0インタフェース 〜ステップ1:USB3.0の概要〜

第24回 低コストFPGAで実現するUSB3.0インタフェース 〜ステップ2:FPGAを用いたUSB3.0の基板設計〜

第25回 低コストFPGAで実現するUSB3.0インタフェース 〜ステップ3:USB3.0 Boardのベンチマーク測定〜

第26回 低コストFPGAで実現するUSB3.0インタフェース 〜ステップ4:USB3.0 Boardのリンク検証事例〜

関連情報

●業界最小コスト、最小消費電力FPGAによるトータル・システム・コストの削減

●Supporting Digital Television Trends with Next-Generation FPGAs[英文](和文は5月上旬リリース予定)

Copyright © ITmedia, Inc. All Rights Reserved.

提供:日本アルテラ株式会社

アイティメディア営業企画/制作:EDN Japan 編集部/掲載内容有効期限:2014年3月31日

FOR FPGA BEGINNERS [PR]

■FPGAとは

■無償ではじめるFPGA設計

FPGA LEARNING CENTER [PR]

FPGAについて、基礎からわかりやすく解説しています。

初級者から熟練者まで、FPGA設計技術を向上させたいすべての人のためのトレーニング講座。

オンライン講座は視聴無料です。

表1:アルテラのFPGAに用意された2種類のメガファンクションの特徴

表1:アルテラのFPGAに用意された2種類のメガファンクションの特徴