第22回 産業機器におけるTCO ―FPGAで回路設計の発想を転換する(後編):FPGA Insights

産業機器業界では、産業用イーサネットの普及や機能安全規格への対応など、大きな市場の変化がある。こうしたトレンドに対応しつつ、企業の収益性をさらに高めていく手法の1つとして、TCO(Total Cost of Ownership:設計資産保有の総コスト)を考慮した製品開発が注目を集めている。前編に続き、本稿ではTCOの削減に向けたFPGAの応用事例などについて解説する。

前回の「FPGAで実現する産業用ワイヤレスセンサーネットワーク」でも述べたが、工場内で使用される産業用ネットワークは「 Fieldbus 」から「イーサネット」をベースとしたネットワークに移行している。工場内にあるドライブ・コントロール・システムなどの機器は、これらの産業用ネットワークに接続されることが多い。MCU といくつかの新しいDSPは、ソフトウエアのオーバーヘッドを使用して(標準の)イーサネット TCP/IP をサポートすることは可能だが、この組み合わせには以下のような問題がある。

- 多くのMCUでは帯域幅が不足しており、DSP は産業用イーサネット/Fieldbus プロトコルと主アプリケーションを同時に処理することができない

- これらのデバイスは多くの場合、『EtherCAT 』、『PROFINET IRT 』、『SERCOS III 』など、一部の 産業用イーサネット・プロトコルが必要とするプロトコル固有のスタックをサポートしていない

- MCU/DSP や ASIC/ASSP は、各プロトコル規格に合わせるための変更を迅速に行うことができない

以上のような理由から、ドライブ・システムをイーサネット・ネットワークにブリッジ接続するには、個別にMCU か FPGA を追加しなければならないことがある。

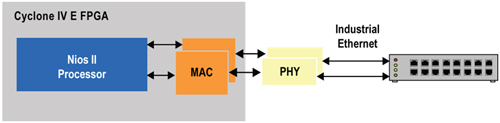

これに対して、FPGA は複数の産業用イーサネット・プロトコル規格を同じプラットフォームでサポートする柔軟性を有し、MCU/DSP のデザインに必要な複数基板を設計するというコストのかかる作業を回避することができる。FPGA は、あらゆる産業用ネットワーク・プロトコル(またはその他の同等の規格)をサポートし、従来の Fieldbus システムをいずれかのイーサネット規格にブリッジ接続できるように再プログラムが可能なため、単一の FPGA プラットフォームをベースとして、複数の製品(イーサネット・プロトコル)に展開することができる(図1)。

制御アルゴリズムをFPGAでハード化

TCO の低減にFPGAがいかに役立つかを示すための事例として、モーター・コントロール・システムを紹介する。電気モーターの動作を制御する半導体チップまたは機能モジュールのモーター・コントローラは、「モーターの起動と停止」、「正回転/逆回転の選択」、「速度の選択と調整」、「トルクの調整または制限」、および「過負荷と障害に対する保護のための手動または自動的な手段」を備えている。

従来のモーター・コントロール・アーキテクチャは、システム・コントローラ、ドライブ・コントロール、モーター、負荷、およびフィードバック・ループで構成されていることが多い。エンコーダやホール効果デバイスなどのセンサーは、サーボ・モーター/アクチュエータの位置または速度の信号をモーション・コントローラにフィードバックして最適なモーター制御をおこなう。

これまで、モーターの技術開発は効率よく、高速に動かす部分にフォーカスされてきた。しかも、事前にプログラムされたシーケンスに従ってモーターを制御するという閉じられたシステムであった。現在は、イーサネットが普及して、単なるシーケンス制御だけではなく、ネットワークを介してリアルタイムにモーターを制御しなければならなくなった。複数のモーターを同時にリアルタイムに制御することも必要となる。これが、従来のアーキテクチャだと、閉じられた世界で制御されているため、タイムロスが発生することもある。

大手の機器メーカーの中には、制御アルゴリズムを自社で開発し、それをASICに展開して機器に実装していたメーカーもいる。しかし、制御アルゴリズムを進化させ、その都度ASICに展開していくとなると、チップの試作や検証が大変である。こういう場合に、FPGAでそのアルゴリズムをハードウエア化して実装すれば、機器のアップグレードが比較的容易である。どうしてもソフトウエア処理が必要な場合は、アルテラ社のソフトウエアプロセッサ「Nios II」をFPGAに組み込めば、必要な機能をワンチップに取り込むことができる。

並列処理でパフォーマンス向上

インテリジェント・ドライブ機能の複雑さ、ドライブ制御軸の数、および製品の機能が増加するにつれて、FOC(Field Oriented Control)アルゴリズムを実行するのに必要な MCU と DSP の処理性能が急速に不足することもある。システムの性能を向上させるために技術者が対応できることは、MCU/DSP の動作周波数を上げ、デバイスが動作限界に達するまでソフトウエア・アルゴリズムを最適化することだけである。

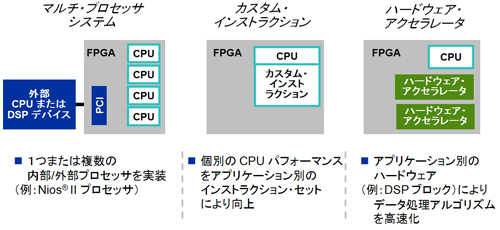

これに対して、FPGAを使用すれば、多軸モーター・コントロールの性能を向上させ、1つのチップにさらに多くの機能を集積することが可能となる。例えば、アルテラ社のFPGA 「Cyclone III/Cyclone IV E ファミリ」では、1 個の FPGA 上に 1 個以上のプロセッサコアを実装してマルチプロセッサ・システムを構築することができる。また、アプリケーション専用の命令セットを作成して、個別プロセッサの性能を向上させることができる。さらに個別アプリケーション向けハードウエアで並列処理を多用して、データ変換アルゴリズムの処理を加速させることも可能だ(図2)。このように、FPGA は、並列信号処理を行うことができることから、モーション・コントロールやモーター・コントロールなどの高速な信号処理を必要とするアプリケーションに適している(図2)。

機能安全・データ・パッケージを用意

自動車製造ライン、包装ライン、印刷工場、石油化学プラントなどで、溶接、切断、穴あけ、化学プロセスなどに用いられる機器は、機能的に安全性が求められる。「機能安全」は、機器の障害によって発生する可能性のある危険に対処して、機械オペレータ、機械装置、および物品が被る可能性がある損害を緩和するために策定された規格である。

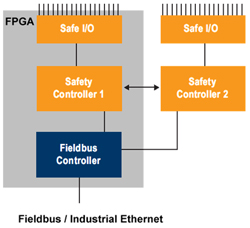

アルテラ社は、機能安全の重要性を早期に認識し、国際認証機関である TUV Rheinland と協力してFPGA業界で初めてとなる機能安全(ファンクショナル・セーフティ)・データ・パッケージを開発し、認証された(図3)。このソリューションはアルテラ社の FPGA、IPコア、および開発ツール「 Quartus II 」で構成される。TUV が認証した機能安全・データ・パッケージを使用すると、安全設計の開発期間と製品認定が最大 2 年も短縮できるようになる。認証を取得するためのリスクを軽減することも可能となる。

本連載では産業機器におけるTCO 削減に向けた、FPGAの応用事例などを解説してきた。FPGA が、製品のライフ・サイクルを通じた開発、機能強化、置き換え、および保守コストに基づいて算定した TCOの削減に寄与する、重要なデバイスの1つであることを理解していただけたと思う。そして、これまでのハードウエア主体の回路設計から、柔軟なシステム設計が可能なFPGAを活用するなど、TCOの削減に向けて設計者自身も発想を転換する好機となろう。

公開中(2010年4月〜2010年12月掲載分)

第9回 トランシーバを内蔵した低コストFPGAの活用法(前編)

第10回 トランシーバを内蔵した低コストFPGAの活用法(後編)

第11回 FPGAの設計開発フロー:〜ステップ1 デザイン設計〜

第12回 FPGAの設計開発フロー:〜ステップ2 制約設定〜

第13回 FPGAの設計開発フロー:〜ステップ3 コンパイル〜

第14回 FPGAの設計開発フロー:〜ステップ4 プログラミング〜

第15回 DDR2 の実装からデバック手法:〜ステップ1 FPGA を用いた DDR2 SDRAMインタフェース〜

第16回 DDR2 の実装からデバッグ手法:〜ステップ2 DDR2 FPGA デザイン設計〜

第17回 DDR2 の実装からデバッグ手法:〜ステップ3 FPGA のデバッグ手法『SignalTap II Logic Analyzer』〜

第18回 DDR2 の実装からデバッグ手法:〜ステップ4 FPGA のデバッグ手法『Debug GUI』〜

第19回 FPGAで実現する 産業用ワイヤレスセンサーネットワーク(前編)

第20回 FPGAで実現する 産業用ワイヤレスセンサーネットワーク(後編)

第21回 産業機器におけるTCO ―FPGAで回路設計の発想を転換する(前編)

第22回 産業機器におけるTCO ―FPGAで回路設計の発想を転換する(後編)

第23回 低コストFPGAで実現するUSB3.0インタフェース 〜ステップ1:USB3.0の概要〜

第24回 低コストFPGAで実現するUSB3.0インタフェース 〜ステップ2:FPGAを用いたUSB3.0の基板設計〜

第25回 低コストFPGAで実現するUSB3.0インタフェース 〜ステップ3:USB3.0 Boardのベンチマーク測定〜

第26回 低コストFPGAで実現するUSB3.0インタフェース 〜ステップ4:USB3.0 Boardのリンク検証事例〜

関連情報

●産業用アプリケーションにおける、設計資産保有の総コストの削減

●アルテラのFPGA で構築する、TUV 認定 機能安全システム

Copyright © ITmedia, Inc. All Rights Reserved.

提供:日本アルテラ株式会社

アイティメディア営業企画/制作:EDN Japan 編集部/掲載内容有効期限:2013年3月31日

FOR FPGA BEGINNERS [PR]

■FPGAとは

■無償ではじめるFPGA設計

FPGA LEARNING CENTER [PR]

FPGAについて、基礎からわかりやすく解説しています。

初級者から熟練者まで、FPGA設計技術を向上させたいすべての人のためのトレーニング講座。

オンライン講座は視聴無料です。