第23回 低コストFPGAで実現するUSB3.0インタフェース 〜ステップ1:USB3.0の概要〜:FPGA Insights

低コストFPGAの登場により、さまざまな用途でFPGAの採用が広がっている。本連載では、FPGAを有効活用してもらうために低コストFPGAに注目し、基本的な「設計開発フロー」や「DDR2 SDRAMの実装手法」を解説してきた。その上で、「産業用イーサネット」への応用や「産業機器におけるTCO」といったテーマについても取り挙げてきた。今回より、低コストFPGAを使い、低リスクで容易に実現することができるUSB3.0インタフェース・ソリューションについて、4つのステップに分けてわかりやすく解説する。

パソコン本体と周辺機器やUSBメモリなどを接続するためにUSBインタフェースが一般的に用いられている。パソコンの高性能化とともに、取り扱うデータの量も膨大となり、このUSBインタフェースも大量のデータを高速に伝送するニーズが高まり、さまざまな通信速度のモードが規格化されている。

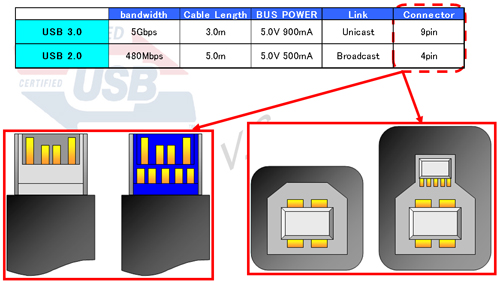

現在、通信速度が1.5Mビット/秒の「Low Speed(LS)モード」(USB1.0)、12Mビット/秒の「Full Speed(FS)モード」(USB1.1)、480Mビット/秒の「High Speed(HS)モード」(USB2.0)が広く普及している。さらに、USB3.0として通信速度が5Gビット/秒の「SuperSpeed(SS)モード」仕様が2008年12月に規格化された。コンプライアンス的にいえばUSB3.0規格に対してホスト側は、すべての通信速度のモードに対応しておく必要がある。これに対してデバイス側は、SSモードとFSモードをサポートしておけばいい。USB3.0はUSB2.0に比べて通信速度が約10倍と高速化した以外でも、仕様の違いがある(表1)。

また、USB3.0はUSB2.0と信号ラインを共有することができないため、デュアルバスアーキテクチャの構成を取っている。このため、USB3.0対応のシステム上ではUSB3.0とUSB2.0のインタフェースは独立して動作する。また、パケットの配信方式も、USB2.0がホスト支配下の全デバイスにパケットを配信するマルチキャスト方式をとっているのに対して、USB3.0はホスト支配下にある特定のデバイスにのみパケット配信を行うユニキャスト方式となっている。

さらに、USB3.0では、Burst転送が新たに追加された。この転送方式はハンドシェイクを待たずにバルク転送を連続的に行うことができるため、大容量/高解像度の画像データを高速に伝送しなければならない用途などに適している。電源管理についても仕様が変更された。それは、ホスト側からの指示に加えて、デバイス側からも省電力モードへの移行を可能としたことである。例えば、トランスミッタ/レシーバをアイドル状態にしたり、PHYの内部クロックを停止したり、パラレルインタフェースのクロックを停止したりすることもデバイス側で行うことができる。

低コストFPGA+PHYチップで実現

USB3.0インタフェースを実現するためには、前述した仕様を満たすハードウエアやソフトウエアを用意する必要がある。まず、ハードウエア的に実現する方法として主に4つある。その1つはブリッジASSPをワンチップで実現することである。すでに、PCI Express Rev.2.0やSATA(Serial Advanced Technology Attachment)とUSB3.0をブリッジするICが商品化されている。

2つ目が低コストFPGAと外付けのUSB3.0/USB2.0対応PHYチップを組み合せる方法である。3つ目はトランシーバ内蔵の高性能FPGAとUSB2.0対応PHYチップの組み合わせである。4つ目はASICで必要なすべての機能をワンチップで実現する方法である。

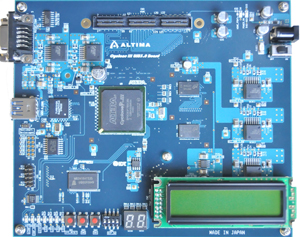

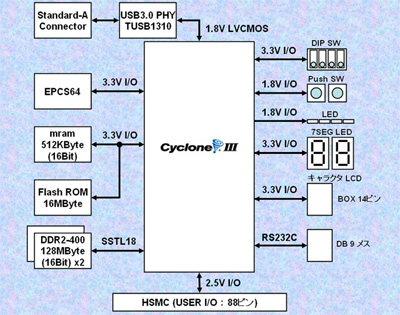

本稿では、USB3.0インタフェースの開発/検証を行うための一例として、アルティマが開発した「USB3.0 Board」(写真1)を使った事例を紹介する。このボードは前述した2つ目の方法で実現している。基板上にはインベンチェアの「Z-Core USB3.0コントローラIP」を組み込んだアルテラ社のFPGA「Cyclone III 」や、TI社のUSB3.0 PHYチップ「TUSB 1310」、NECエンジニアリングの「デバイス・ドライバ/アプリケーション・ソフトウエア」などが実装されている。

このボードの特徴は、上位層とPHY層の部分を2つに分けることで、低コストのFPGAを利用することができる点だ。このボードを利用することで、ホスト側、デバイス側の両方のUSB3.0インタフェースを検証することができる。

FPGAとPHYチップ間は、SSモード用の「PIPE III 」インタフェースとHS/FS/LSモード用の「ULPI 」インタフェースで接続される。PIPE III は周波数が250MHz・SDRで16ビット/32ビット構成、ULPIは60MHz・SDRで8ビット構成である。特に、PIPE III は周波数が高いため、信号品質を十分に確保するための回路設計に注意することが必要だ。設計経験の浅いエンジニアには伝送シミュレーションの利用をお勧めする。例えば、シミュレータとしては、メンターグラフィックス社の「HyperLynx」などがある。

USB3.0 Board(写真1参照)の中央部に実装されているのがCyclone IIIである。その左側にUSB3.0 PHYチップが、さらにその左側にUSB3.0のコネクタ(Standard A)がそれぞれ配置されている。また、FPGAの上部にはイーサネットやDVIなどのインタフェースボードを拡張できるメザニンカード用のコネクタ(HSMC)も用意されている。その回路ブロックを図1に示す。

Cyclone IIIをベースとしたUSB3.0 Boardを、USB3.0インタフェースの開発/検証に活用するメリットは以下のとおりである。

- USB3.0 PHYチップを外付けで使うことにより、低コストFPGAでもUSB3.0インタフェースの検証が可能となる。

- このボードを使用して、回路基板の作成とIPの評価、ソフトウエアの開発を並行して同時に行える。

- HSMCコネクタが用意されているため、アルテラから供給されているDVIやHDMI、SD/HDなどのドータ・カードによる拡張が容易に行える。

- ホスト側とデバイス側の両方のソリューションを検証することができる。

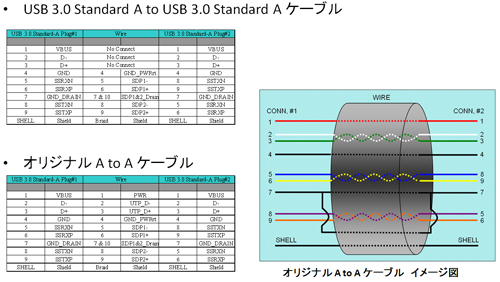

さらにアルティマでは、独自のA to Aケーブルをホシデンと共同開発し供給している(図2)。これによって、USB3.0とUSB2.0の2つのインタフェースを1本のケーブルで対応することができる。電源供給はジャンパーピンで切り替えを行う。例えばホスト側を検証するには、ジャンパーピンでつなぎ、デバイス側を検証する場合にはジャンパーピンを外すだけで済む。

ステップ1では、USB3.0とUSB3.0 Boardの概要について述べた。次回のステップ2では、USB3.0インタフェースを開発する際の、プリント基板の回路設計とパターン設計のガイドラインについて、わかりやすく解説する。

公開中(2010年4月〜2010年12月掲載分)

第9回 トランシーバを内蔵した低コストFPGAの活用法(前編)

第10回 トランシーバを内蔵した低コストFPGAの活用法(後編)

第11回 FPGAの設計開発フロー:〜ステップ1 デザイン設計〜

第12回 FPGAの設計開発フロー:〜ステップ2 制約設定〜

第13回 FPGAの設計開発フロー:〜ステップ3 コンパイル〜

第14回 FPGAの設計開発フロー:〜ステップ4 プログラミング〜

第15回 DDR2 の実装からデバック手法:〜ステップ1 FPGA を用いた DDR2 SDRAMインタフェース〜

第16回 DDR2 の実装からデバッグ手法:〜ステップ2 DDR2 FPGA デザイン設計〜

第17回 DDR2 の実装からデバッグ手法:〜ステップ3 FPGA のデバッグ手法『SignalTap II Logic Analyzer』〜

第18回 DDR2 の実装からデバッグ手法:〜ステップ4 FPGA のデバッグ手法『Debug GUI』〜

第19回 FPGAで実現する 産業用ワイヤレスセンサーネットワーク(前編)

第20回 FPGAで実現する 産業用ワイヤレスセンサーネットワーク(後編)

第21回 産業機器におけるTCO ―FPGAで回路設計の発想を転換する(前編)

第22回 産業機器におけるTCO ―FPGAで回路設計の発想を転換する(後編)

第23回 低コストFPGAで実現するUSB3.0インタフェース 〜ステップ1:USB3.0の概要〜

第24回 低コストFPGAで実現するUSB3.0インタフェース 〜ステップ2:FPGAを用いたUSB3.0の基板設計〜

第25回 低コストFPGAで実現するUSB3.0インタフェース 〜ステップ3:USB3.0 Boardのベンチマーク測定〜

第26回 低コストFPGAで実現するUSB3.0インタフェース 〜ステップ4:USB3.0 Boardのリンク検証事例〜

関連情報

●低コストで実現!次世代インタフェース、USB 3.0・・・(1)

●アルティマ、国内初*「低コストFPGAで実現するUSB3.0ソリューション」を発表[プレスリリース]

Copyright © ITmedia, Inc. All Rights Reserved.

提供:日本アルテラ株式会社

アイティメディア営業企画/制作:EDN Japan 編集部/掲載内容有効期限:2013年3月31日

FOR FPGA BEGINNERS [PR]

■FPGAとは

■無償ではじめるFPGA設計

FPGA LEARNING CENTER [PR]

FPGAについて、基礎からわかりやすく解説しています。

初級者から熟練者まで、FPGA設計技術を向上させたいすべての人のためのトレーニング講座。

オンライン講座は視聴無料です。