第20回 FPGAで実現する 産業用ワイヤレスセンサーネットワーク(後編):FPGA Insights

工場などの生産現場においても、「イーサネット」や「ワイヤレス通信」によるネットワークの構築が進んでいる。本稿では、産業用途向けワイヤレス通信規格である「WirelessHART」または 「SP100.11a」に対応した、柔軟性の高い通信インタフェース機能を工場内ネットワーク機器に実装するための手法として、FPGAを応用した例について紹介している。前編では産業用イーサネットと産業用向けワイヤレス通信規格の概要や、ゲートウェイの主要回路ブロックと設計時の課題などについて述べた。後編では産業用ワイヤレスセンサーネットワーク向けのFPGA設計フローなどについて解説する。

前編でも述べたように、すでに複数の通信プロトコルが存在している産業用イーサネットをベースとしたネットワークに、各種フィールド機器をワイヤレスで接続しようとすると、通信プロトコルの組み合わせが複雑となる。その上、プロトコル自体の進化にも対応しなければならず、これらのネットワークをブリッジする機能を、従来のプロセッサや専用のASICを用いて実現しようとすると、ハードウエア/ソフトウエアの開発には多大な労力が必要となる。

FPGAの設計フロー

こうした課題を解決する方法の1つがFPGAの活用である。柔軟性の高いFPGAを使用すれば、複数の産業用イーサネット規格に対応できる回路を比較的容易に設計することができる。ここではアルテラ社のFPGAを使って、その設計フローやIPコアの活用事例を紹介する。

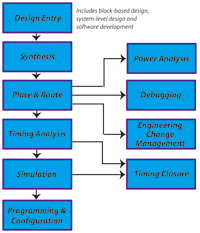

FPGAコンフィギュレーションファイルは、アルテラ社の開発ソフトウエア「 Quartus II 」などのツール群によって生成される。アルテラ社から供給されるこのソフトウエアは、VHDL、Verilog、回路図、グラフィック、あるいはブロックベースの設計方式によるFPGAコンフィギュレーションの設計、変更、生成に必要なすべてのものを提供している。この設計環境では、ハードウエア・シミュレーションツールへのインタフェース、ハードウエア・ランタイムデバッグツール、システムパフォーマンス/消費電力最適化機能などがサポートされている。これによって、従来のFPGA設計フローに比べて生産性を格段に高めることができる(図1)。

FPGAベースのハードウエア設計

プリビルドプロセッサとイーサネットMAC IPコアは、比較的簡単に入手することができるようになった。このため、SOPC(System On a Programmable Chip)とビルダツール(Quartus II スイートに含まれる)を使って、簡単にカスタムプロセッサとイーサネットMACを実装したハードウエア設計を行うことが可能となった。GUI指向のビルダツールは、IPベースのシステムの構成、統合、生成を加速し、ハードウエア設計の自動化を支援している。このため、経験の浅い技術者でも設計を比較的容易に行える。

このビルダツールは構築するシステム用のすべてのHDLを生成できるため、手作業によるコーディングが不要である。さらにはテスト済みのIPがプリビルドされていることや、システム相互接続が自動生成されることから、ミスのない設計が行える。生成されたシステムをコンパイルするのも簡単で、作成されたコンフィギュレーションファイルをすぐにFPGAにダウンロードすることができる。

新しい設計または設計の変更が必要となった場合には、GUIを使用して簡単に設計を修正することができる。あとはシステムを再生成し、再コンパイルするだけだ。したがって、新しい産業用イーサネット・プロトコルに対応するためのハードウエア設計は、単に必要な産業用イーサネット IPを購入し、それを既存のシステム設計に組み込んで再生成するだけで作成できる。ワンクリックで再コンパイルすれば、ハードウエア設計ができあがる。

産業用イーサネットハードウエアとソフトウエアIP

前編でも紹介したように、現在は「Modbus/TCP」、「EtherNet/IP」、「PROFINET」、「ETHERNET Powerlink」、「SERCOS III」、「VARAN」「EtherCAT」といった多くの産業用イーサネット・プロトコルが存在し、それに対応したIPパッケージが市販されている。ハードウエアIPは通常、MACやその他必要なロジックを含んだSOPCビルダコンポーネントとしてパッケージングされている。ソフトウエアIPは、Nios II 組み込みプロセッサ向けにC言語で記述されたライブラリまたはソフトウエアAPIとして提供されている。

開発キットでプロジェクト開始

開発プロジェクトを始めるためのもっとも簡単な方法は、産業用イーサネット開発キットを活用することである。産業用イーサネットシステム向けの実証済み開発ボードソリューションとリファレンス設計は多くのベンダーから提供されている。これらのボードには、低価格のFPGAとデュアルチャネル産業用イーサネットEE802.3 Layer 1イーサネット通信ハードウエアが搭載されているため、IPプロトコルには依存しない。CANやUSB、UART、LVDSといった他のインタフェース用のトランシーバが搭載されている場合もある。

低価格で柔軟性の高いFPGAやソフト・プロセッサIP、プリビルドされた産業用イーサネットハードウエアならびにソフトウエアIPが登場したことにより、ワイヤレスシステムをさまざまな規格の産業用イーサネットネットワークに接続できるプログラマブルソリューションの開発が可能となった。FPGAは、同一ハードウエアを使って様々な産業用イーサネット通信プロトコルに対応できるほか、プログラマブルデバイスの利点を活かしたシステムの統合、柔軟性、陳腐化の防止を実現することができる。そしてFPGAを使用することのもう1つのメリットは、必要なすべての機能が1つに統合された開発環境を使用することで、開発期間が短縮され、システムの保守が容易になり、産業用イーサネットベースのネットワーク用ICの設計を最小限の労力で簡単に作成できるようになったことである。

公開中(2010年4月〜2010年12月掲載分)

第9回 トランシーバを内蔵した低コストFPGAの活用法(前編)

第10回 トランシーバを内蔵した低コストFPGAの活用法(後編)

第11回 FPGAの設計開発フロー:〜ステップ1 デザイン設計〜

第12回 FPGAの設計開発フロー:〜ステップ2 制約設定〜

第13回 FPGAの設計開発フロー:〜ステップ3 コンパイル〜

第14回 FPGAの設計開発フロー:〜ステップ4 プログラミング〜

第15回 DDR2 の実装からデバック手法:〜ステップ1 FPGA を用いた DDR2 SDRAMインタフェース〜

第16回 DDR2 の実装からデバッグ手法:〜ステップ2 DDR2 FPGA デザイン設計〜

第17回 DDR2 の実装からデバッグ手法:〜ステップ3 FPGA のデバッグ手法『SignalTap II Logic Analyzer』〜

第18回 DDR2 の実装からデバッグ手法:〜ステップ4 FPGA のデバッグ手法『Debug GUI』〜

第19回 FPGAで実現する 産業用ワイヤレスセンサーネットワーク(前編)

第20回 FPGAで実現する 産業用ワイヤレスセンサーネットワーク(後編)

第21回 産業機器におけるTCO ―FPGAで回路設計の発想を転換する(前編)

第22回 産業機器におけるTCO ―FPGAで回路設計の発想を転換する(後編)

第23回 低コストFPGAで実現するUSB3.0インタフェース 〜ステップ1:USB3.0の概要〜

第24回 低コストFPGAで実現するUSB3.0インタフェース 〜ステップ2:FPGAを用いたUSB3.0の基板設計〜

第25回 低コストFPGAで実現するUSB3.0インタフェース 〜ステップ3:USB3.0 Boardのベンチマーク測定〜

第26回 低コストFPGAで実現するUSB3.0インタフェース 〜ステップ4:USB3.0 Boardのリンク検証事例〜

関連情報

●デモ: FPGA 1チップで、複数の産業用イーサネット・プロトコルをサポートする方法

Copyright © ITmedia, Inc. All Rights Reserved.

提供:日本アルテラ株式会社

アイティメディア営業企画/制作:EDN Japan 編集部/掲載内容有効期限:2013年3月31日

FOR FPGA BEGINNERS [PR]

■FPGAとは

■無償ではじめるFPGA設計

FPGA LEARNING CENTER [PR]

FPGAについて、基礎からわかりやすく解説しています。

初級者から熟練者まで、FPGA設計技術を向上させたいすべての人のためのトレーニング講座。

オンライン講座は視聴無料です。