第24回 低コストFPGAで実現するUSB3.0インタフェース 〜ステップ2:FPGAを用いたUSB3.0の基板設計〜:FPGA Insights

FPGAを有効に活用してもらうための事例の一つとして、本連載では低コストFPGAを使ったUSB3.0ソリューションを紹介している。前回のステップ1ではUSB3.0の概要を取り上げた。本稿では、ステップ2として、低コストFPGAとUSB3.0対応のPHYチップを実装したUSB3.0インタフェースの基板設計におけるガイドラインをわかりやすく解説する。

USB3.0インタフェースに対応する回路設計において、「SuperSpeed (SS) ライン」と「PIPE III(PHY Interface for PCI Express III)ライン」の2つの信号ラインを設計する際には、特に注意する必要がある。SSラインは、PHYチップとコネクタを接続するための配線で、USB3.0用コネクタで新たに追加された5ピンの部分である。USB2.0で対応しているHigh Speed (HS)ラインの転送レートは480Mビット/秒である。これに対して、SSラインの転送レートは5Gビット/秒と10倍速い。

SuperSpreedライン

SSラインは、転送レートが5Gビット/秒のPCI Express rev.2.0と類似点が多く、差動パターンやGNDパターン、ビア、スルーホールなど配置・配線の制約に関しては、PCI Expressにおける設計情報やノウハウを参考にすることができる。

SSラインの設計に関して、配線長の制約条件などについてはUSB Implementers Forumの資料に詳細な指示が記載されているので参照していただきたい。例えば、デバイス側のPHYチップとコネクタの配線長は2.54cm〜15.24cmと明記されている。また、テキサス・インスツルメンツ(TI)のデータシートには、配線インピーダンスや線長誤差の許容範囲、TXラインのACカップリングに使うキャパシタの仕様などが記載されており、設計時の参考となるであろう。

デバイス側には一般的に「Standard-B」コネクタが用いられる。PHYチップとStandard-Bコネクタを接続する場合は、ピン配置を考慮して5Gビット/秒のSSラインを優先して配線の設計を行ったほうがいい。そのあとでUSB2.0用のデータ線を配線すれば、クロストークを削減することができる。

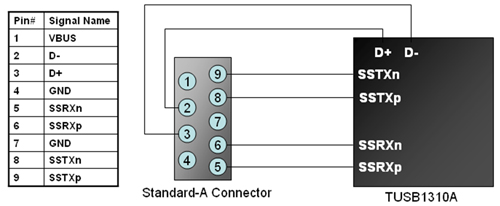

PHYチップと「Standard-A」コネクタを使用する場合は工夫が必要である。アルティマはUSB3.0 Board(写真1)を設計する際に、コネクタのSSTXp(9ピン)端子をPHYチップのSSTXn端子に、コネクタのSSTXn(8ピン)端子をPHYチップのSSTXp端子に、それぞれ接続している(図1)。PIPE III(USB3.0)では極性反転をサポートしており、この機能を使うことで、プリント基板上において差動信号をクロスさせる必要がなくなるからだ。

また、USB3.0規格に対応したコネクタは、プリント基板に実装すると基板の裏面から端子(足)がはみ出してしまう。裏面からはみ出した余分な部分は基板実装後に切断してスタブを除去する。コネクタとPHYチップの配線はボトム層で行う。USB3.0 Boardでは、GNDでシールドした。さらに、D+/−(HS/FS/LSライン)はコネクタ端子の周りを回避するように配線している。

PIPE IIIライン

USB3.0対応PHYチップとFPGA間のインタフェースには、PIPE IIIとULPIが用いられる。PIPE IIIでは、125MHz・SDR×32ビット構成、250MHz・SDR×16ビット構成、500MHz・SDR×8ビット構成のいずれかをとることができる。USB3.0 Boardでは、使用したPHYチップの仕様に合わせて250MHz・SDR×16ビット構成とした。一方、HS/FS/LS用のインタフェースであるULPIは、60MHz・SDR×8ビット構成である。特にPIPE IIIインタフェースは転送速度が250MHzと高速なため、設計には十分に注意を払うことが必要だ。

伝送シミュレータで事前検証

PIPE III インタフェースの設計にあたり、アルティマではまず、トポロジーの検証を行った。PIPE IIIのトポロジーを検証する方法としては、全ての信号線にダンピング抵抗を挿入して検証する方法などがあるが、そのためには、FPGAとUSB3.0対応PHYチップを接続するための「PCLK」や「TX_DATA」、「TX_DATAK」、「RX_DATA」、「RX_DATAK」などの信号線に挿入する抵抗値や検証方法などについての十分な知識が必要となる。アルティマでは、USB3.0 Boardを設計するときに、FPGAの内部抵抗を利用するとともに、伝送線路シミュレータを利用して検証を行った。

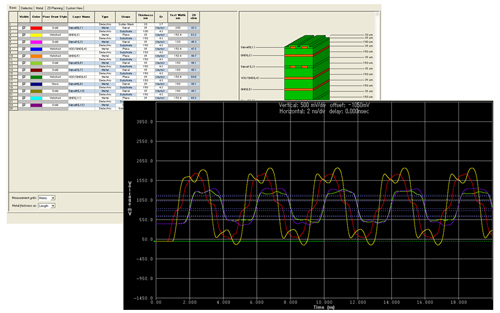

PIPE IIIを設計する際、技術者によっては、これまで行ってきた回路設計の経験則だけでは対応が難しいかもしれない。このようなケースでは、伝送線路シミュレータで事前に検証することが問題を解決する近道となることが多い。アルティマではUSB3.0 Boardを設計するにあたって、Mentor Graphicsの「HyperLynx SI」を使って検証した。シミュレータを適用したのは、設計フローの中で2か所ある。まず、FPGA設計でピン配置が終わり、回路図設計を行う際に伝送線路のシミュレーションを実施した。そして、レイアウト作業が完了した時点で最終チェックのためにシミュレータで確認している。2か所で検証することによって、設計フローの後工程における手戻しを出来る限り少なくできるからだ。

伝送線路シミュレータを活用する利点は大きく2つある。その1つは抵抗値やコンデンサの容量、配線長を事前に見積もることが可能である。このため、それぞれの数値をその場で変更して検証することができる。その際、FPGAは最終的に設計データをチップに実装するためにコンパイル作業を行わなければならないが、コンパイル作業は比較的時間を要することもあるので、出来る限りコンパイル前にシミュレーションを行ったほうがいい。

2つ目は、伝送路の任意の場所にプロービングして信号の波形を観測することができることだ。実機の場合、BGAなどパッケージの形状によっては物理的にプロービングができないこともある。また、プローブ自体が信号品質に影響を与える可能性もある。シミュレーションではこういった実機での問題を心配する必要がない。

開発ツールからIBISモデルを自動生成

シミュレーションを行うには、そのためのモデルが必要となる。代表的なシミュレーション・モデルとしてはIBIS(Input/Output Buffer Information Specification)やSPICE(Simulation program Integrated circuit emphasis)がある。一般的にIBISはクロック周波数が1GHz未満のシミュレーション用に適している。SPICEは高い精度が要求される場合や1GHz以上のシミュレーション用として利用されることが多い。USB3.0 Boardの設計においては、クロック周波数が250MHzであったためIBISモデルを使ってシミュレーションを行った。なお、シミュレーションに必要なモデルは、主要なチップベンダーのウェブサイトからダウンロードして入手することができる(参考1、参考2)。今回のUSB3.0 Board設計においては、HyperLynx用のIBISモデルをアルテラの開発ツール「Quartus II 」から自動生成した。これによって生成されたIBISモデルであれば、制約条件などを新たに設定する必要がない。

HyperLynx SIを用いてPIPE IIIインタフェースの伝送線路を検証した(図2)。上述の通り、Quartus IIから自動生成されたIBISモデルには、ピン名や制約条件がすでに反映されている。シミュレーションの操作も簡単である。画面上に表示されたピンをダブルクリックして、IBISモデルを選択する。次に伝送線路にダンピング抵抗を挿入するか否かを設定する。USB3.0 Boardの設計ではFPGAの内部抵抗を用いている。

今回はSSラインとPIPE IIIラインの2つの信号ライン設計について述べた。次回はUSB3.0 Boardのベンチマーク測定について分かりやすく解説する。

公開中(2010年4月〜2010年12月掲載分)

第9回 トランシーバを内蔵した低コストFPGAの活用法(前編)

第10回 トランシーバを内蔵した低コストFPGAの活用法(後編)

第11回 FPGAの設計開発フロー:〜ステップ1 デザイン設計〜

第12回 FPGAの設計開発フロー:〜ステップ2 制約設定〜

第13回 FPGAの設計開発フロー:〜ステップ3 コンパイル〜

第14回 FPGAの設計開発フロー:〜ステップ4 プログラミング〜

第15回 DDR2 の実装からデバック手法:〜ステップ1 FPGA を用いた DDR2 SDRAMインタフェース〜

第16回 DDR2 の実装からデバッグ手法:〜ステップ2 DDR2 FPGA デザイン設計〜

第17回 DDR2 の実装からデバッグ手法:〜ステップ3 FPGA のデバッグ手法『SignalTap II Logic Analyzer』〜

第18回 DDR2 の実装からデバッグ手法:〜ステップ4 FPGA のデバッグ手法『Debug GUI』〜

第19回 FPGAで実現する 産業用ワイヤレスセンサーネットワーク(前編)

第20回 FPGAで実現する 産業用ワイヤレスセンサーネットワーク(後編)

第21回 産業機器におけるTCO ―FPGAで回路設計の発想を転換する(前編)

第22回 産業機器におけるTCO ―FPGAで回路設計の発想を転換する(後編)

第23回 低コストFPGAで実現するUSB3.0インタフェース 〜ステップ1:USB3.0の概要〜

第24回 低コストFPGAで実現するUSB3.0インタフェース 〜ステップ2:FPGAを用いたUSB3.0の基板設計〜

第25回 低コストFPGAで実現するUSB3.0インタフェース 〜ステップ3:USB3.0 Boardのベンチマーク測定〜

第26回 低コストFPGAで実現するUSB3.0インタフェース 〜ステップ4:USB3.0 Boardのリンク検証事例〜

関連情報

●低コストで実現!次世代インタフェース、USB 3.0・・・(1)

●アルティマ、国内初*「低コストFPGAで実現するUSB3.0ソリューション」を発表[プレスリリース]

Copyright © ITmedia, Inc. All Rights Reserved.

提供:日本アルテラ株式会社

アイティメディア営業企画/制作:EDN Japan 編集部/掲載内容有効期限:2013年3月31日

FOR FPGA BEGINNERS [PR]

■FPGAとは

■無償ではじめるFPGA設計

FPGA LEARNING CENTER [PR]

FPGAについて、基礎からわかりやすく解説しています。

初級者から熟練者まで、FPGA設計技術を向上させたいすべての人のためのトレーニング講座。

オンライン講座は視聴無料です。