SoC vs.マルチチップ:「集積」と「分割」の正しい見極め(2/3 ページ)

集積か、分割か

ここでは、筆者が調査した集積と分割の具体例を紹介する。これらの具体例から、どのような観点で分割が行われているのかが見て取れるはずだ。

■性能

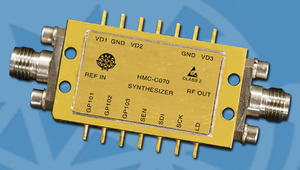

米Hittite Microwave社は、製造プロセスの特性や、エンジニアリング能力、コスト、製造数量、設計の変動性といった要件に基づき、集積レベルを決定する。例えば、同社が製造する高性能マイクロ波シンセサイザモジュールは、最高の性能を実現するために、3種類の異なるプロセス技術で製造した複数のチップから構成されている(写真1)。

また、同社は、2つのチップを1つのQFNパッケージに集積したPLL(Phase Locked Loop)製品を製造している。VCO(電圧制御発振器)には、最高性能を引き出すためにGaAsプロセス技術を適用し、それ以外のPLL機能にはシリコンチップを使用している。

一方、「一般消費者向けの製品のように、低コストであることと小サイズであることが求められる場合には、微細なCMOSプロセス技術を用いるのが適切だ」とHittite社は考えている。例えば、自動車のレーダー検出器には通常、単一のCMOSチップが使用される。厳しいコスト要件により、それ以外に実用的な選択肢がないからだ。

Hittite社のPLL製品は、6GHz未満の周波数で動作するものは単一のCMOSチップで実現し、それ以上の周波数が求められるものは複数のチップに分割することで実現されている。マルチチップ構成にすることによってGaAsプロセス技術を用いることが可能になるので、最大26GHzもの周波数で動作する製品が供給されている。

■耐圧

Analog Devices社の高精度アンプ担当アナログ製品ラインディレクタを務めるSteve Sockolov氏は、機能ごとに別のチップに実装すべきケースが存在する理由を説明してくれた。「アンプは、プリント基板の端かコネクタ上に配置することが多い。このことから、顧客が8kVのESD(静電気放電)耐圧を要求してくるケースがある。そのレベルに耐えられる大きさの対ESD構造を微細なプロセス技術で実現することも不可能ではない。しかし、コスト的には適切なことではない」(同氏)という。さらに、「多くの顧客は、40Vという電源の過電圧耐性を求めるが、微細プロセスではそれを実現することはできない」と同氏は指摘する。

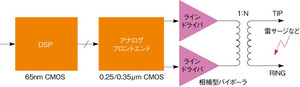

同社のADSL(Asymmetrical Digital Subscriber Line:非対称デジタル加入者線)向けラインドライバは、図2のようにトランスとともに使用する。このトランスは、ツイストペア電話回線上に40Vの信号を伝送する。大型の昇圧トランスを用いるなら、低電圧動作のラインドライバを使用することができるが、それでは入力信号が小さくなり、システムの性能が低下してしまう。それに対し、Analog Devices社のラインドライバは12Vまたは24Vで動作するので、トランスでは1次巻線と2次巻線の比率をほぼ1対1とすることができる。このラインドライバには、落雷に対して電話回線を保護する役割も求められる。落雷は、1msの間に50Vも変化する電圧と、6Aにも達するサージ電流を引き起こす可能性がある。同社で高速ネットワークアンプ担当製品ラインディレクタを務めるJim Doscher氏によると、微細CMOSプロセス技術では、この規模のサージには耐えられないという。

■遅延の最小化

アナログ信号処理を専門とする新興企業の米GTronix社でCEO(最高経営責任者)を務めるHubert Engelbrechten氏は、「マルチチップ構成にすると、遅延を削減することができる」と述べている*7)。例えばハードディスクドライブのヘッドアンプは、ノイズを除去し、出力信号がノイズの影響を受けないように働く必要がある。この要件を満たすためには、移動するリードヘッド上にアンプが存在するのが理想である。同様に、DVDプレーヤの中のレーザードライバも、移動するピックアップ上に存在する必要がある。負荷に近い位置に配置できれば、配線のインダクタンスが抑えられ、遅延を削減することが可能になる。

米Fairchild Semiconductor社は、同社のDrMOS(driver MOS)製品にこの原理を適用している。ドライバをパワーFETと同一パッケージに搭載することで、スイッチング速度を高めている。

■プリント基板の面積

Samplify Systems社は、医療機器向けのアナログフロントエンドICを製品化している。1つのチップに16個のA-Dコンバータチャンネルを集積した製品だが、低ノイズアンプとプログラマブルゲインアンプは集積していない。

一方で、同等の機能を備えたICをシングルチップで提供している競合他社も存在する。その競合企業は、「当社のICを用いるほうが、部品点数が少なくなり、設計が簡素化される。さらに、インピーダンスやカップリングに関する問題が解消されるので、設計が容易になる」と顧客に主張してきた。

Samplify Systems社で医療/画像製品担当マーケティングディレクタを務めるDanny Kreindler氏は、「最初は競合他社の製品に飛びついた顧客もいたが、現在ではシングルチップのソリューションを回避し始めている」と指摘する。その上で、「実は、マルチチップのほうが、シングルチップを用いるよりもプリント基板を小さくできることが多い。さらに、消費電力を削減できるケースも多々ある」(同氏)と付け加えた。

■消費電力

消費電力の削減も、分割を選択する理由の1つである。Analog Devices社のSwan氏は、「システムを全体的にとらえて、システム全体の消費電力を低減可能な最良の方法を考える必要がある」と述べる。その上で、同氏は、オンボードの加速度計を用いて動きを検知する低消費電力チップの例を紹介してくれた。この例における電源管理チップは、バックライトを点灯させるとともに、ユーザーによりキーがアクティベーションされたことを回路が検出できるように働く。これを利用して、大きなデジタルチップは動作が必要になるまで停止させておくことで、無駄な電力消費を回避するのである。

これと同様の理由に基づき、英Wolfson Microelectronics社は、携帯機器向けの製品群においてチップを分割し、オーディオサブシステムと電源管理機能を1つのアナログICに搭載するというアプローチをとっている。

■処理の性質の違い

携帯電話機の設計者は、デジタルシステムに区分される領域の処理を、ベースバンドプロセッサとアプリケーションプロセッサという2つの大きなチップに分割する。ベースバンドチップでは、遅延が小さく、割り込みが生じないことが求められる。一方、アプリケーションプロセッサでは、数ms程度の遅延は問題にならない。

電源管理コンサルタントであるPaul Greenland氏は、「ベースバンドチップでは、複雑なプロトコルに対するエラー訂正や復調の処理が非常に多く行われる。そのため、ユーザーアプリケーション機能は別のチップで行う必要がある」と述べる。

■デジタル−アナログの分割

「微細なCMOSプロセス技術では、多くのアナログ回路で必要となる電圧/電流特性が得られない」とGreenland氏は指摘する。そこで、アナログ回路をデジタル回路に置き換えることができれば大きなメリットが生まれる。同氏は、「デジタルのPWM(パルス幅変調)ループは、アナログのPWMループの1/6~1/4の面積で実現できる」と述べる。つまり、アナログ部とデジタル部にうまく分割できればコストメリットが得られるのだ。

米Exar社は、セットトップボックスやサーバー向けのデジタル電源チップにこの手法を適用している。同社の知的財産(IP:Intellectual Property)/特許には、小型ICの製造手法に関するものが多い。同社は、デジタル電源チップにチャージポンプのハイサイドドライバは集積するが、パワーFETは集積しない。これにより小型化を実現し、アナログ製品にコストで対抗できるようにしている。同時に、アナログチップにはないプログラマビリティと通信機能を提供する。

脚注

※7…Rako, Paul, "Analog floating-gate technology comes into its own," EDN, Dec 15, 2009, p.29

Copyright © ITmedia, Inc. All Rights Reserved.