ツールで確保するシグナルインテグリティ(1/3 ページ)

シグナルインテグリティの問題は、注意を怠ると後で災いとなって返ってくる。専用のソフトウエアツールを利用することにより、設計のなるべく早い段階で、その問題を回避するようにすることが肝要だ。本稿では、シグナルインテグリティへの対処の流れを簡単に説明した上で、各種ベンダーが提供するツールにはどのようなものがあるのかを紹介する。

高速化で露見した問題

ICやシステムインターフェースの設計は、電子機器に高速シリアルチャンネルが使用されるようになってから大きく変化した。SERDES(Serializer/Deserializer)、DDR(Double Data Rate)2/3、PCI(Peripheral Component Interconnect)、USB(Universal Serial Bus) 3.0など、高速バスのシリアルリンクは、1ギガビット/秒(Gbps)を超える通信速度を実現する。当初、これらは、スーパーコンピュータ、通信インフラ、パソコンなどに使用されていたが、現在では民生用機器にまで高速シリアルチャンネルが搭載されるようになっている。

数Gbpsの速度では、デジタル信号であってもアナログ領域のものとして扱わなければならなくなる。信号が決して論理レベルの1に達しない場合もあれば、ICのパッケージや、FR-4のプリント配線板(以下、基板)上のトレース、コネクタ、ケーブルを通った後に、論理レベルの1を大きく超える場合もある。逆に、信号が論理レベルの0に達しないこともあれば、グラウンドレベルを下回るケースもある。

米Sigrity社の製品マーケティングマネジャを務めるKen Willis氏は、「シリアルリンクでは、ビアやビアスタブのようなものの扱いが非常に重要になる。GHz以下のレベルでは問題にならなかったことが、GHz以上のレベルになると非常に大きな意味を持つ」と述べる。

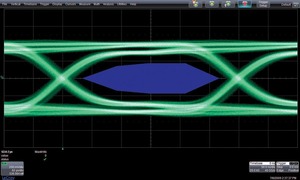

高速シリアルリンクにおけるシグナルインテグリティの問題は、経験豊富な設計者にとっても、後になって災いとして返ってくる可能性のある厄介な存在である。シリアルチャンネルのトラブルシューティングは、クロック信号のような反復的な信号によって行うことはできない。信号の忠実度(fidelity)には、信号のデータパターンが影響を与えるからである。PRBS(擬似ランダムバイナリシーケンス)信号をチャンネルに入力し、データ依存の問題やISI(シンボル間干渉)があれば、それらを解消しなければならない。その際には、PRBS信号を入力し、得られた波形を重ね合わせて生成したアイダイアグラムを観測すればよい(写真1)。

設計/評価の基本プロセス

米Mentor Graphics社のビジネス開発マネジャであるDavid Wiens氏は、「大まかな経験則に従い、直ちにプロトタイプの開発に取り掛かる人は、すぐに問題に突き当たる可能性が高い」と述べている。問題の起きない設計を行うには、チャンネルのシミュレーションを行うための高度なソフトウエアツールと、リンクを構成するコンポーネントのシミュレーションモデルを抽出/作成するための補助ソフトウエアツールが必要である(図1)。ここで、抽出の作業には、ハイエンドのシリアルデータ用オシロスコープとベクトルネットワークアナライザの使用が不可欠となる。

BER(ビット誤り率)を許容可能なレベルに抑えられるリンクが得られたら、続いてはリンク間にクロストークが生じていないことを確認する必要がある。クロストークが存在すると、新たな問題が生じるからだ。

システム全体が稼働したら、システムの高速信号からの放射が大き過ぎないことを確認する。放射が大きいと、そのシステムをFCC(米連邦通信委員会)のRFI(無線周波数干渉)/EMI(電磁干渉)の規格に合格させることができない。Mentor社のビジネス開発マネジャを務めるSteven McKinney氏によると、「シミュレーションの手段を持たない企業の90%が、規格への準拠の問題を解決するために、再スピンや、ほかの手法の採用を余儀なくされている」という。基板の再設計や市場への投入の遅れを回避するには、高度なシグナルインテグリティツールを導入しなければならない場合が多い。

シリアルリンクのシグナルインテグリティを評価するには、テストベンチで実際にハードウエアを使ってシグナルインテグリティを測定/評価するという困難な作業が必要になる。チャンネルの通信速度は非常に高速であるため、測定用プローブによる負荷の問題などが原因で、シグナルインテグリティの劣化が発生しないように注意しなければならない。また、実機の測定でアイダイアグラムを取得したとしても、例えば受信機チップが信号を処理するために適用するのと同じイコライゼーションを適用しなければ、そのダイアグラムは無意味なものとなる。こうした問題に対処するには、米LeCroy社、米Tektronix社、米Agilent Technologies社、アンリツなどのベンダーが供給する高度なシリアルデータアナライザが必要になる。

ソフトウエアベースのシミュレータを使い始めたとしても、複雑な作業はさらに続く。ソフトウエアツールでは、伝送系のモデル化が必要になる。IC用のものとしては、ドライバ、レシーバや、イコライゼーション、プリエンファシスの効果をモデル化するために、IBIS(Input/Output Buffer Information Specification) AMI(Algorithmic Modeling Interface)がよく用いられる。IBISモデルは、送信端子の動作を時間ベースで記述したテーブルから成る。これは、Sパラメータが、マルチポートシステムにおける周波数領域の動作を表したテーブルで構成されるのに似ている。

IBISモデルのより高度な機能であるAMIは、実行可能なコードとして表すことができる。つまり、受信機ICのための高度なイコライザや送信機ICのためのプリエンファサイザを開発するICメーカーは、これらのアルゴリズムを実行可能なファイルとして扱うことができるということだ。この機能を利用することで、高度なオシロスコープやネットワークアナライザとIBISモデルを連携させ、チップが生成するイコライゼーションの効果のようなチャンネルの性能を観測することが可能になる。

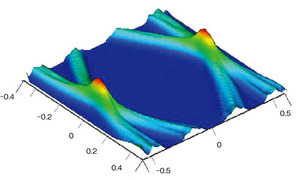

損失のないFR-4基板上の差動ペアについてであれば、容易にシミュレーションすることができる。しかし、残念ながらシグナルインテグリティの問題に対処するには、数十〜数百ものペアをシミュレーションし、その本質的なパフォーマンスだけでなく、チャンネルが互いに与え合う影響についても調査する必要がある。また、近くにある電源などに現れる高速デジタル信号の影響をモデル化しなければならないケースもあり得る。いずれにせよ、ソフトウエアツールにより、時間領域と周波数領域の両方の手法を用いて、シグナルインテグリティの解析を行う必要がある。また、統計的解析を適用し、チャンネルのBER、EMI放射、RF耐性に対するジッターやクロストークの影響を予測しなければならないこともあるだろう(図2)。

Copyright © ITmedia, Inc. All Rights Reserved.