車載システムを変える“スマートパワーSoC”:低コスト化の鍵としての可能性を探る(1/2 ページ)

インドTata Motors社の低価格車「Nano」に代表されるように、自動車開発においては低コスト化が大きなポイントとなっている。筆者らは、この低コスト化の鍵を握るものとして、「スマートパワーSoC」という概念を提案したい。本稿では、このスマートパワーSoCのコスト面における優位性を明らかにするとともに、モーターやLED照明の制御に適用した事例を紹介する。

モーター/センサーを200個搭載

現在量産されている自動車は、多数のモーターとセンサーを搭載している。モーターであれば、一般的な乗用車1台につき40個程度、高級車では70〜120個のモーターが搭載されている*1)。また、加速度、圧力、電流などのさまざまな値を検知するセンサーは、トヨタ自動車の「プリウス」の場合で100個以上搭載していると言われている。つまり、自動車1台につき、モーターとセンサーが合計で150〜200個搭載されているわけだ。そして、これらのモーターとセンサーを制御するには、同じ数のドライバICも必要になる。あるいは、ヘッドライトやルームランプなどの各種照明用途にLEDを利用する動きも加速しており、その場合にはLED用のドライバICも必要になる。

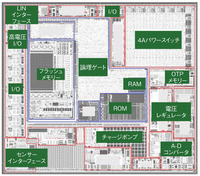

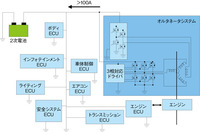

こうした各種ドライバICを代替するものとして、筆者らは「スマートパワーSoC(Systen On Chip)」を提案したい(図1)。スマートパワーSoCとは、以下のような回路/機能を備えた半導体製品のことである。

■LIN(Local Interconnect Network)やセンサー信号などの入出力を行うインターフェース

■CMOSロジックプロセスで製造できるプロセッサコア、RAM、ROM、フラッシュメモリーなど

■電源IC、OTP(ワンタイムプログラマブル)メモリー、A-Dコンバータなど、耐圧60VまでのアナログICの機能

■数Aの電流を制御できるドライバICの機能

これらは、自動車システムの制御を行うコンピュータユニットであるECU(電子制御ユニット)に搭載されている機能とほぼ同じである。つまり、スマートパワーSoCを用いることにより、1個のICをECUとして機能させることが可能になるのだ。それが難しい場合でも、ECUの小型化、低コスト化や、生産ラインの簡略化を実現できるようになると考えられる。

BCDプロセスで製造

スマートパワーSoCは、マイクロプロセッサやロジックICの製造に用いられているCMOSロジックプロセスではなく、アナログ/パワー半導体の製造にも対応するBCD(Bipolar CMOS DMOS)プロセス*2)を利用して製造される。BCDプロセスは、CMOSロジックプロセスのマスクセットに、バイポーラプロセスやDMOSプロセスに対応する数枚のマスクを加えた形のものとなる。

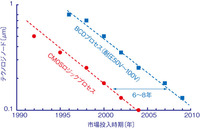

また、BCDプロセスの微細化のロードマップは、最先端のCMOSロジックプロセスと比べて、3〜4世代、つまり6〜8年遅れている(図2)。車載向けに用いられるBCDプロセスであれば、さらに2年遅れていると言われている。

このことは、BCDプロセスのベースとなるCMOSロジックプロセスの部分には、歩留りが安定していて、減価償却が完了した生産設備を再利用できるということを意味している。この場合、最先端のCMOSロジックプロセスを用いるのと比べて、製造コストは約1/2に抑えることが可能だ。

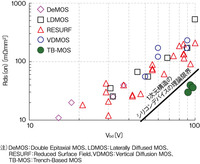

これに加えて、スマートパワーSoCの進化を語る上で欠かせないのが、バイポーラプロセスやDMOSプロセスの進展である。1990年代からさまざまな改良が加えられており、構造の堅牢さを維持しながら、微細化と低コスト化をともに実現している。例えば、ディープトレンチアイソレーション(DTI)や、DMOSプロセスにおけるオン抵抗Rds(on)の低減(図3)、動作温度範囲を規定するジャンクション温度Tjの上限の拡張などである。

スマートパワーSoCの車載要件

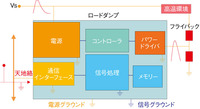

ここでは、車載用途のスマートパワーSoCに求められる要件について説明する。重視される要件は、電源と負荷に対する出力(以下、負荷出力)、通信インターフェースに対するノイズ耐性である(図4)。

■電源と負荷出力

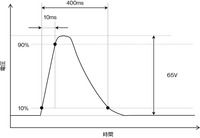

自動車のECUにおいて、電源と負荷出力の端子に加わる代表的なノイズとして広く知られているのが、オルタネータ(発電機)から発生するロードダンプである。

一般的な自動車の内部で用いられる電力は、3相全波整流回路を用いたオルタネータから供給される(図5)。この車内唯一の電力源であるオルタネータが、ECUを破壊するレベルの大電流パルスを発生させることがある(図6)。これがロードダンプである。ロードダンプという名称は、一斉にロード(負荷)がダンプする(オフになる)際、オルタネータなどのインダクタンスにより発生することから付けられた。

ロードダンプは、オルタネータの3相全波整流器において、ツェナーダイオードを使ってクランプすることで回避できる。クランプ電圧は、半波で17V、グラウンドに対しては34Vとなる。クランプしない場合には、65Vもの電圧によるロードダンプがスマートパワーSoCの電源部に印加されることになる。

■通信インターフェース

車載ネットワークのプロトコルとして広く知られているのが、エンジンやトランスミッションなどのパワートレインシステムや、ステアリング、ブレーキなどのシャーシシステムを中心に用いられているCAN(Controller Area Network)と、窓の開閉や座席の動作などボディ制御系システムに用いられているLINである。

ノイズの多い環境下で用いられるこれらの車載ネットワークのプロトコルには、高い信頼性が要求される。特に、LINの仕様では、「26.5Vまたはグラウンドショートのとき、ECUにダメージなきこと」という仕様が存在する。そのため、LINのインターフェースにはパワー半導体と同レベルの耐性が求められる*3)。

製造コストが大幅に低減

自動車では、ECUを設置するスペースが限られている。もし、消費電力が大きい高性能のICをECUに搭載しようとしても、そのICが発する熱を十分に冷却できない可能性がある。このため、一般的に、ECUに搭載するICに許容される消費電力は数W、消費電流は数Aまでとなる。

一方、ECUを含めた自動車の各システムの定格電圧は12Vである。この12Vのシステムで必要となる耐圧性能は、先に述べたロードダンプの要件から60V〜80V程度になる。スマートパワーSoCに用いられるBCDプロセスは、消費電力、消費電流、耐圧性能に対するこれらの要件を満足しており、車載用途で用いるのに最適だと言えよう。

BCDプロセスを用いたICの導入が始まったのは1990年代からである。プロセスルールは2.5μmで、当初はアナログ/パワー半導体の機能のみを集積していた。つまり、スマートパワーSoCではなく、「スマートパワーIC」にすぎなかった。

例えば、当時のABS(アンチロックブレーキシステム)のBOM(部品表)コストで見ると、スマートパワーICと車載マイコンのコストはほぼ同額だった。逆に言えば、ECUに搭載するマイコンの値段に応じて、それと同等のコストがスマートパワーICに充てられていたとも言える。

しかし、現在では、BCDプロセスの主流は0.35μm〜0.25μmにまで進化している。プロセスの微細化によってチップに集積できる機能が増え、スマートパワーSoCと呼べるものが中核を成すようになったのである。

微細化による最大の変化は、CMOSロジックプロセスによる部分のコストが劇的に減少したことだ。これによって、ハードウエアロジックの機能の多くをチップ上に搭載できるようになった。16ビットのプロセッサコアのゲート数は約2万個で、チップ面積の1/10を占める程度にすぎない。そういう意味では、プロセッサやロジック回路の機能は、アナログ/パワー半導体に付加された“おまけ”のようにも考えられる。しかし、機能面では、ICに大きな差異化をもたらしてくれる。

現在のスマートパワーSoCは、以前と比べてパッケージコストも激減した。1990年代に広く用いられていた大型のパワー半導体のパッケージに代わって、2000年代に入ってからは、車載用途でもリードフレームが外に露出しているEP(Exposed Package)デザインのSOP/QFNパッケージが主流となっている(写真1)。パッケージコストは、50米セントから10米セントへと、約1/5に低減された。一方で、パッケージのサイズが著しく小さくなったにもかかわらず、放熱性能も保たれている。

脚注

※1…アスモ、製品紹介ページ、http://www.asmo.co.jp/product/

※2…BCDプロセスは、Bipolar、CMOS、DMOSを用いた、特に、車載用で使われるアナログミックスドシグナルプロセスの通称。半導体メーカー各社で名称が異なるが、オン・セミコンダクタの場合、スマートパワープロセスと呼んでいる。本稿では、国内で広く使われているBCDプロセスという名称を使用する。

※3…LIN Specification package revision 2.1、http://www.lin-subbus.org/

Copyright © ITmedia, Inc. All Rights Reserved.