UARTのボーレートをDDSで生成:Design Ideas

UARTのボーレートのクロックは、多くの場合、あり合わせの発振器を使用することで生成できる。本稿では、UARTのボーレートをDDSで生成する方法を紹介する。

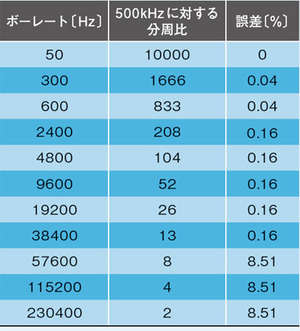

UART(Universal Asynchronous Receiver Transmitter)のボーレートのクロックは、多くの場合、あり合わせの発振器を使用することで生成できる。所要のボーレートを得るには、発振器からのクロックを分周することになるが、この分周処理によってボーレートに誤差が生じることになる。表1は、8MHzの水晶発振器からのクロックを16分周した500kHzのクロックと通常のバイナリカウンタを利用してボーレートを発生させた場合に生じる誤差を示したものである。ボーレートの誤差は、発振器の周波数がボーレートとうまくマッチしていない場合に大きくなる。この手法でも、18.432MHzで動作する発振器を使用することができるならば、誤差をゼロに抑えるように分周比を設定することが可能である。

上述した分周回路によるボーレート生成手法に代わるものとして、DDS(Direct Digital Synthesizer)を用いる手法がある。これであれば、同じ8MHzの水晶発振器を使用してボーレートをより高くした場合でも、誤差を小さく抑えることが可能である。例えば、20ビットのDDSを使用した場合の誤差は、表2のようになる。以下では、この手法について説明するが、DDSの基本的な動作の説明は本稿では割愛するので、それについては参考文献*1)などを参考にされたい。

図1は、矩形波出力のみを備える、ごく基本的なDDSの構成例である。矩形波出力は、位相アキュムレータのMSB(最上位ビット)から取り出せばよい。また、図のように2分周のステージを付加することにより、最終的な信号のデューティを50%とすることができる。このような構成において、ボーレートのクロック周波数は、DDSにおける制御値と位相アキュムレータのビット数Nを使って以下の式から計算すればよい。

ボーレートクロック=(基準クロック×制御値/2N)/2

位相アキュムレータを20ビット、制御値(tuning_word)を16ビットとしてボーレートの発生器を構成する場合のVerilogサンプルコードは、http://www.edn.com/file/25467-Modified_DDS_functions_as_baud_rate_generator_listing.docからダウンロードすることができる。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング