水晶発振器の使い方:「水晶発振器」活用の手引き(3)

前回までに、水晶発振器の特性を決定づける水晶振動子と発振回路の基本、ならびに水晶発振器の特性項目(仕様)について説明した。今回は、水晶発振器の使い方の基本について解説する。トラブルを発生させることなく水晶発振器を使いこなすためには何を知っておくべきなのか、そのポイントをまとめてみたい。

電源デカップリングは重要!

半導体デバイスの電源デカップリングがなぜ重要なのかということについては、『デカップリングコンデンサの選び方、使い方』で詳細に説明した。本連載における定義によれば(第1回目を参照)、水晶発振器は、水晶振動子と、半導体デバイスとして構成される発振回路を1つのパッケージにまとめて製品化したものである。従って、水晶発振器についても、電源デカップリングはその使用法の基本として最優先で実行されるべきことである。

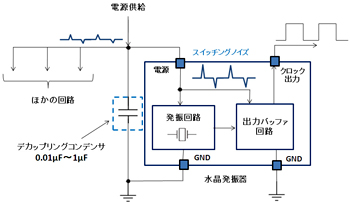

図8に、水晶発振器の簡易ブロック図と、デカップリングコンデンサを含む周辺回路の接続例を示した。電源デカップリングの目的は、IC自身で発生するノイズ成分の除去、電源ライン上のノイズ成分の除去、IC相互間のノイズ干渉の防止である。水晶発振器では、水晶にエネルギーを供給することで発振を安定して継続させる。結果として、水晶発振器は、数百kHz〜100MHz程度の周波数で大振幅のクロックを発生させる。この挙動から、水晶発振器は1つのノイズ源ともなり得る。その発振動作によって電源に影響を及ぼすし、出力バッファ回路によるクロック出力動作は、周辺回路に対しても影響を与える。

水晶発振器に含まれるロジック素子については、一般に、発振器内部での電源/グラウンドへの接続において、電源デカップリングは施されていない。すなわち、水晶発振器の電源/グラウンドには、発振周波数およびその高調波成分がスイッチングノイズとして存在することになる。このことは、システム設計においてかなり重要なポイントである。電源デカップリングを行わないと、水晶発振器と同一の電源によって動作するすべての回路に、水晶発振器のスイッチングノイズが伝達されてしまう。ロジック回路であればその影響の度合いは小さいとも言えるが、アナログ回路では、その精度、動作に直接影響を及ぼしかねない。

電源デカップリング用のコンデンサとしては、積層セラミックコンデンサを使うとよい。スイッチングノイズの周波数を考慮し、コンデンサのデータシートに記載されているインピーダンス‐周波数特性のグラフを参照して最適な容量値を決定することを推奨する。

電源デカップリング用のコンデンサは水晶発振器に対して最短距離で接続する。それにより、プリント基板の配線パターンによるインピーダンスの影響で、デカップリングの効果が減少することを最小限に抑えなければならない。

水晶発振器の電源デカップリングについて整理すると、次のようになる。

- 水晶発振器には電源デカップリングを施す

- デカップリングコンデンサとしては積層セラミックコンデンサを使用する。容量値は、除去したい周波数に対するインピーダンス特性を考慮して決定する

- デカップリングコンデンサは、水晶発振器に最短距離で接続する

クロック出力までの遅延時間

水晶発振器の内部では、その製品の発振周波数、電源電圧、出力レベルといった仕様に適合したロジック素子が用いられている。最終的なクロックを出力するバッファ回路などがそれに当たり、この部分は純然たるロジック回路である。従って、CMOSベースの水晶発振器であれば、ハイ/ローいずれかのレベルの出力状態しか存在しない。

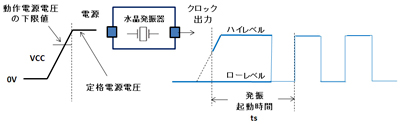

図9に、水晶発振器に供給する電源電圧とクロック出力の遷移の様子を示した。水晶発振器に電源が投入されてから、所定のクロックが出力されるまでの時間は、発振起動時間、発振開始時間などとして仕様で規定されている。製品ごとに条件は異なるが、一般的には、規定されている電源電圧範囲の下限値(5V系の製品で動作電圧範囲が4.5V〜5.5Vの場合であれば4.5V)に、実際の電源電圧が達したタイミングを基準(スタート時間:0)とし、実際にクロックが出力されるまでの時間tsが定義されている。

また、クロックが出力されるまでの間は、水晶発振器の出力はハイレベルまたはローレベルの固定された状態となる。そして、発振開始時間tsが経過した時点で、安定したクロック出力が得られる。このことは、システム設計において、水晶発振器の出力クロックを受け取る側の各デバイスが、電源が投入されてから実際に動作するまでのタイミングにも大きく影響する。特に、初期リセット(イニシャライズ)動作のためにクロックを必要とするICにおいては重要な要素となる。電源投入時のシーケンスとしては、以下の2つが考えられる。

- 水晶発振器のクロック出力が安定してから、ほかの回路にクロックを供給

- ほかの回路が安定した後に、水晶発振器のクロックを供給

これらのうちどちらを選択するかは、システム構成によって決定される。いずれにしても、水晶発振器では、電源の投入からクロック発振出力が得られるまでには遅延時間があること、クロックが出力されるまではハイ/ローいずれかのレベルに出力が固定されていることを認識しておかなければならない。

なお、水晶発振器の中でも、より高度な機能を備える水晶発振モジュールでは、発振のオン/オフを制御する機能や、トライステート出力の制御機能を備えるものなどがある。これについては次回、説明する予定である。

電源とクロックの立ち上がりについて整理すると次のようになる。

- 水晶発振器において、電源が投入されてからクロックが出力されるまでには遅延時間がある

- 遅延時間についての規定や条件は製品ごとに異なる

- クロックが出力されるまでは、出力はハイ/ローのいずれかのレベルに固定されている

- 実際のアプリケーションでは、ほかの回路とのタイミングの整合性を考慮してシーケンスを決定しなければならない

負荷による波形への影響

水晶発振器の出力は、一般的なロジックICと同じく、TTLとCMOSに大別することができる。水晶発振器に接続される負荷についての特性/仕様も、出力部に使用されているロジック素子の特性で決定されている。重要なのは、クロックのハイ/ローレベルを正確に認識するための条件を、実際のアプリケーションにおいても確実に実現することである。

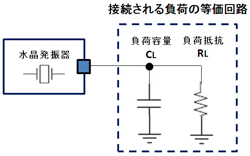

図10に示したのは、水晶発振器に接続される負荷の等価回路である。TTL出力では、負荷がTTLロジックICである場合、そのICで規定されているハイ/ローレベルにおける出力/入力電流が流れる。これについて、図10では負荷抵抗RLによって表現されている。この負荷抵抗RLは等価回路であるわけだが、接続可能なTTLの数は、通常はファンアウト数として規定されている。

一方、CMOS出力では、負荷がCMOSロジックICである場合、そのICにはほとんど電流は流れ込まない。影響を及ぼすのは、負荷として働くそのICの容量である。これは図10においては、負荷容量CLで表現されている。実際の水晶発振器製品では、許容負荷容量の値が規定されている。

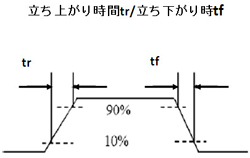

また、水晶発振器においては、出力クロックの立ち上がり時間trと立ち下がり時間tfが図11のように定義されている。この図は、クロック振幅の10%から90%まで立ち上がるのにかかる時間がtr、同90%から10%まで降下するのにかかる時間がtfと定義されている場合の例である。パーセンテージについての規定は製品ごとに異なるが、ほとんどの場合、図11のような10%、90%の組み合わせか、20%、80%の組み合わせのいずれかである。

クロック出力の立ち上がり時間trと立ち下がり時間tfについては、負荷容量CLの値が必ず条件として示されている。逆に許容負荷容量CLについては、クロック出力の立ち上がり/立ち下がり時間を満足し得る条件として規定されている。これらが何を意味しているかと言うと、「水晶発振器の出力波形は負荷条件の影響を受ける」ということである。実際のアプリケーションにおいては、水晶発振器から見た等価インピーダンスである負荷容量CLと負荷抵抗RLが、出力クロック波形に総合的に影響を及ぼすことに注意しなければならない。

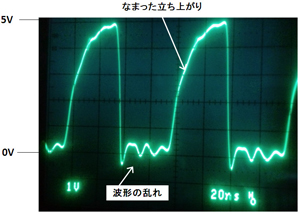

具体的な例として、写真1に、標準的な水晶発振器のクロック出力波形を示した。これは、オーディオ用D-Aコンバータのボードに実装された水晶発振器の出力を実測したものである。そのボードでは、発振周波数が12.288MHz、電源電圧が5Vという条件で水晶発振器を動作させていた。水晶発振器の負荷としては、S/PDIF(Sony Philips Digital Interface)デコーダICとSRC(Sample Rate Converter) ICが切り替えスイッチを介して接続されている。写真1から明らかなように、クロック波形の立ち上がりはやや緩やかなっている(なまっている)。立ち下がりは急峻だが、波形に乱れ(アンダーシュート)が生じていることが確認できる。

ここで、水晶発振器に接続されたロジックICのハイレベルの閾(しきい)値電圧VIHが、TTLのICであれば2.0V以上、CMOS ICであれば4.0V以上であったとしよう。写真1の立ち上がりの部分を見ると、2V付近は急峻だが、4V付近では緩やかである。接続されるICがCMOSであるとすると、TTLの場合よりも、クロック入力に遅延が生じていることになる。

写真1の波形は、水晶発振器がプリント基板に実装された状態で観測したものである。従って、目に見える負荷であるICとスイッチのほかに、クロックラインのパターンによる浮遊容量も負荷として存在している。実際の設計においては、このようなプリント基板の配線パターンの影響も十分に考慮する必要がある。

負荷条件に関して整理すると次のようになる。

- 水晶発振器の負荷条件に関する仕様と条件は必ず確認する。TTLではファンアウト数、CMOSでは許容負荷容量がこれに当たる

- 水晶発振器の出力クロック波形(立ち上がり時間/立ち下がり時間)は、負荷条件の影響によって変化する

- 水晶発振器の総合的な負荷容量には、実装先であるプリント基板の配線パターンの浮遊容量も含まれる。実装時のクロック波形は必ず確認する

最適な実装パターンとは?

ここまでに解説したとおり、水晶発振器の基本的な使い方としては、まず電源デカップリング、電源‐クロック出力のシーケンス、負荷条件によるクロック波形などについての確認を行う。その上で、必要に応じた対処を実施することが重要である。水晶発振器の実装を行う上では、電源デカップリングにおける一般的な注意点をそのまま適用することになる。また、負荷に対するパターンも、負荷容量の観点から重要な要素となる。

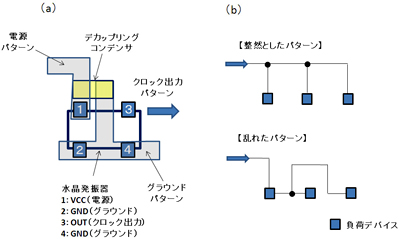

図12(a)に示したのは、水晶発振器の実装パターンの推奨例である。ここでは、4端子の表面実装型水晶発振器の例を示している。各グラウンド端子は共通のグラウンドパターンに接続し、電源端子から最短距離でデカップリングコンデンサを配置している。水晶発振器自身の動作については、この推奨パターンに従えば問題が発生することはないはずだ。

もう1つの重要な要素は負荷の接続パターンである。図12(b)では、3個の負荷デバイスに接続する例を「整然としたパターン」と「乱れたパターン」として示している。クロックを供給(接続)するという目的は同じでも、両者の間には大きな差異があり、水晶発振器から見た負荷容量が異なっている。結果的に、負荷デバイスの入力部での波形の乱れ具合にも違いが現れる。当然、「整然としたパターン」のほうが優れている。

クロック出力と、負荷となるデバイスは、なるべく最短距離で接続することを推奨する。ある程度距離が長くなる場合には、クロックラインにグラウンドガードを設けるのもよい。クロックラインのパターンがアンテナとなり、EMI(電磁干渉)や相互干渉を防ぐという意味では効果的だ。ただし、一方では、グラウンドガードによるパターンによって浮遊容量が増え、負荷容量が大きくなるので注意が必要である。この辺りは、システム設計時に考慮しつつ、試作段階で実装回路によって確認しながら対処するほうが確実だと言える。

実装条件について整理すると次のとおりである。

- 水晶発振器の実装パターンは図12のようなものとする

- 出力クロックの負荷接続パターンは整然としたパターンとする

- クロックラインが長くなる場合にはグラウンドガードを設ける。このことは、EMIや相互干渉の観点からは有効であるが、負荷容量が大きくなる点には注意を要する

Copyright © ITmedia, Inc. All Rights Reserved.