回路シミュレータの最新動向を探る(前編):SoCの不具合を見逃さないために(2/2 ページ)

デジタル回路検証の標準規格

Mentor Graphicsで検証/試験プロダクトのマーケティングディレクターを務めるSteve Bailey氏によると、「現在、EDAツールにおけるシミュレータの市場は成熟しつつある。同市場の焦点は、迅速かつ完全な検証によって技術者を支援できるようなシミュレータの開発に移っている」という。シミュレータの解析速度や精度は、マルチコアCPUを用いた並列処理などの手法によって向上してはいるが、どの手法も特効薬にはなり得ていない。これらの手法を利用するとしても、設計した回路を適切に分割した上で、分割した回路のそれぞれに最適な解析ツールを用いることは容易ではないからだ。

Mentorは、顧客を対象に行った最近の調査で、ハードウエア記述言語と検証言語を統合したHVL(Hardware Verification Language)の1つであるSV(System Verilog)を使用する割合が予想以上に多いという結果を得た。回答者の3/4が、テストベンチの作成にSVを使用している、あるいは使用する予定があると回答したという。また、SVの採用が制限される理由の1つとして、EDAベンダーのツール間において互換性がないことが挙げられた。市販されている検証ツールでSVを用いる際には、シミュレータとテストベンチのライブラリに互換性があることを確かめる必要がある。

現在、EDA業界は、デジタル回路検証用の基本機能ライブラリについて標準化を進めている。この標準化作業の中で、最も注力されているのが移植性の問題である。Bailey氏によると、「EDAツールの業界団体であるAccelleraが、最新の機能検証手法の標準規格としてUVM(Universal Verification Methodology) Version 1.0 EA(Early Adopter)を策定できた事実は、複数の企業の検証ツールにおいて最初に導入されたSVをベースにした手法が成熟しつつあることを示している」と述べている。機能検証の標準規格といえば、MentorのAVM(Advanced Verification Methodology)から始まり、続いてMentorとCadenceが共同開発したOVM(Open Verification Methodology)が登場した。そして、UVMは、OVMをベースに、Synopsysが開発したVMM(Verification Methodology Manual)を規格に取り込んでいる。

Synopsysで検証プロダクトのマーケティングディレクターを務めるMichael Sanie氏は、「当社は、Synopsys Fellowを務めるVMMの専門家のJanick Bergeron氏を代表とするグループをAccelleraに派遣して、UVMの規格開発に向けた取り組みに参加した」と明かす。UVMには、メモリーやメモリーマップドレジスタ用のRAL(レジスタ抽象化レイヤ)アプリケーションパッケージなどのVMMの機能が取り入れられている。Synopsysは、2011年5月にも、同社の検証ツール「VCS」でのUVM 1.0 EAのネイティブサポートを提供する予定だという。Sanie氏は、「VCSはすでにOVMをサポートしているので、テストベンチの移植のためにUVMをサポートするバージョンのリリースを待つ必要はない」と付け加えた。同氏は、「検証ライブラリ用の基本クラスの記述方法は、ツールの差異化の主な要因にはならない」と考えている。EDAツールベンダーは、今後もシミュレータの解析エンジンの性能向上やデバッグツールの投入によって、優位に立つための競争を続けることが予想される。

プロパティ/テストパターンの自動生成

検証技術者は、設計したICのプロパティの試験について、SVを用いたアサーションベース検証(ABV)手法であるSVA(System Verilog Assertion)によって行うことができる。SVAでは、詳細な記述ができるほかに、ランダム入力パターンに対する制約を定義したり、カバレッジの解析方法を決定したりすることができる。

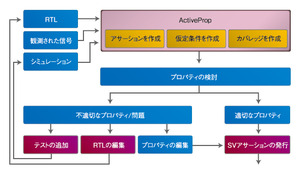

Jasper Design Automationのツール「ActiveProp」は、設計した回路のRTL(レジスタトランスファレベル)の記述からプロパティを自動的に生成することができる。そのほかに、VCD(Value Change Dump)やFSDB(Fast Signal Database)形式のシミュレーション結果を準備するだけでよい。

Jasperでマーケティング担当バイスプレジデントを務めるHolly Stump氏によると、「ActivePropが自動生成するフォーマル(形式的)解析、シミュレーション、エミュレーション向けのアサーションによって、即座にABVを始めることができる」という。ActivePropはスタンドアロンでも使用できるし(図1)、実行時にAPI(Application Programming Interface)を介してシミュレータにリンクすることもできる。複数のシミュレーションを実行すれば、それらの結果からプロパティを自動生成することにより、ABVの精度をさらに高めることもできる。なお、ActivePropの最初のバージョンは、Synopsysのシミュレータに対応している。

ActivePropは、設計した回路データ(RTL記述)を入力すると、そのRTL記述の中から重要なものを抽出して示してくれる。通常、RTL記述からプロパティを生成するためには、RTL記述の機能ブロックにおける重要な信号線などを識別した上で、信号についても注意深く調べる必要がある。ActivePropは、この作業を自動化しているのである。次に、ActivePropは検討用の候補の数を減らすためにプロパティを分類したりまとめたりしたものを作成する。その出力形式は、人間が読める状態で記述されたレポートのほか、SVの制約条件やアサーション、カバレッジなどとなっている。

UVMは、検証手法として、制約条件のもとでランダムに生成したテストパターンを使用するランダム検証手法などを採用している。これよって、人手で作成したテストパターンを使用するディレクテッド検証より検証カバレッジを向上させることができる。ただし、生成されたテストパターンの冗長部分を除去することも重要である。

こうした問題に対して、Mentorは、テストベンチのコンポーネントの作成に使用できるテストベンチ自動化ツール「inFact」を提供している。inFactにおける、テストベンチのコンポーネントの動作は「ルールグラフ」と呼ばれる機能によって制御されている。ルールグラフのルールは、検証中のデバイスの仕様から定義することが可能だ。例えば、業界標準バスインタフェースなどのほか、検証プランから抽出した制約条件を適用することもできる。シミュレーション実行時には、ルールグラフがシミュレータと対話を行い、要求された機能カバレッジを効果的に達成できるように高度なアルゴリズムを適用する。また、inFactは、複数のプロセッサコアを用いた並列処理にも対応している。MentorのBailey氏によると、「あるinFactのユーザーは、同ツールを用いることでカバレッジの達成時間を約1/100に短縮できた。また、カバレッジの割合も向上した」という。

後編では、回路エミュレータやアナログ回路とデジタル回路の協調シミュレーションの分野における、EDAツールベンダーの最新の取り組みについて紹介する。

Copyright © ITmedia, Inc. All Rights Reserved.