回路シミュレータの最新動向を探る(後編):SoCの不具合を見逃さないために(2/2 ページ)

アナ/デジ協調シミュレーション

0か1の2値で表わされるデジタル回路のブーリアン性質は、アナログである実世界において実現不可能な一定の自動化や抽象化を行うのに有用である。Verilog-AMSなどのAMS(アナログミックスドシグナル)モデリング言語が登場してから10年以上になるが、アナログ回路のシミュレーションや解析には現在でもSPICEやFast SPICEが主に使用されている。アナログ回路を扱うSPICE/Fast SPICEシミュレータと、デジタル回路を扱うHDLシミュレータを連携させて行う協調シミュレーションは、アナログ回路とデジタル回路の相互作用を解析することが必要なミックスドシグナル回路の動作を検証する場合に効果的な手法といえる。

すべてのSoCは、電源管理回路やクロック回路、高度な信号処理ブロック、A-D変換ブロックなどに、シミュレーションや検証が必要な何らかの形のアナログ回路が組み込まれている。SoCのテストベンチにSVを使用する比率が高まる中で、アナログ回路とデジタル回路の両方に対応できるように、SVをAMSの検証用に拡張するためのさまざまな取り組みが行われている。

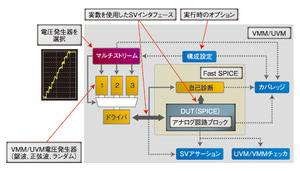

SynopsysのAMS対応テストベンチは、アナログ回路ブロック用に新しい構成を加えることによってVMMとUVMを拡張した(図4)。まず、同社はSVに関する独自の機能を検証ツールである「VCS」に追加した。そして、同社のAMS対応の回路シミュレータ「CustomSim」との協調シミュレーションによって回路動作をチェックするテストベンチにおいて、SVを扱えるようにした。SynopsysでCustomSimのプロダクトマーケティングマネジャーを務めるBradley Geden氏は、「このAMSテストベンチでは、VCSと、CustomSim内に統合されたFast SPICEエンジン『NanoSim』や『XA』との協調シミュレーションをサポートする」と説明する。

このAMSテストベンチでは、VCSを使って、アナログ回路の電圧や電流の読み出し/書き込みを行ったり、値を実数に変換したりするシミュレーションが行える。ただし、離散的な区分定数化を行った実数モデルを用いるシミュレーションと比べると、処理速度と精度を両立させることができない点で劣る。なぜなら、実際の回路の協調シミュレーションは、実行時にAMSテストベンチにアナログ値を供給するからだ。AMSテストベンチでは、クロックを持たないほとんどのアナログ回路動作に適応する非同期の相互作用を観測できる。

また、AMSテストベンチのコンポーネントには基本クラスの波形発生器やチェッカが含まれている。テストパターンはカスタマイズ可能で、正弦波や鋸波、方形波の発生器をツールが提供している。プレビルト(あらかじめ作成された)チェッカにより、しきい値や安定度、周波数、スルーレートなどの、一般的なアナログ回路の動作を測定することができる。AMSテストベンチでは、SVで規定されたランダムテストパターンをアナログ信号に適用でき、ミックスドシグナル処理をSVクラスとしてモデル化できる。さらに、SVモニターをアナログ信号に適用して、SVAを使って確認できる。VMMを最上位のテストベンチとして使用すれば、ほかのシミュレータで実行可能なことを確認する必要があるような複雑なテストシーケンスも検証に取り入れることができる。

アナログ信号の非同期サンプリングを実行する場合には、Synopsysが改良したVerilog-AMSのcross関数である「@(snps_cross())」を使用できる。Verilog-AMSに関しては、シミュレーション性能に対する影響を少なくするために信号のサンプリングレートを最小化しなければならない。AMSテストベンチの中でDUTを具体的に示せば、VCSは自動的にe2r(electrical-to-real)変換とr2e(real-to-electrical)変換を実行してくれるだろう。電圧やポート電流の値を取得あるいは印加するのに必要な、SPICEまたはVerilog-AMS回路の階層にあるすべてのノードへのアクセスも可能である。

アナログ信号にSVAを適用するためには、AMSテストベンチ上で同期モニターと非同期モニターの両方を作成する必要がある。同期モニターを作成するには、デジタル回路シミュレータのクロックを使用してテストを起動する。非同期モニターに対しては、アナログ回路シミュレータがテストを起動できるようにするためのシステム関数をSynopsysが追加している。

Verilog-AMSを拡張へ

Freescale SemiconductorのAMS検証技術者でAccelleraのVerilog-AMSアサーション小委員会の会長を務めるScott Little氏は、「アナログ検証とデジタル検証の仲介を行うととともに、デジタル回路におけるUVMに相当するようなAMSのモデルに対するニーズがある」と指摘する。同委員会は、連続的かつリアルタイムな動作と、UVMのような離散時間におけるデジタル回路向けの標準規格を融合できるように、SVの定義を拡張しようとしているのだ。Little氏は、「検証技術者が用いる、回路シミュレータやテストベンチなどの“ツールボックス”の精度をさらに高めるための努力をしている」とした上で、「デジタル検証技術者が、アナログとの境界にぶつかったときに、その問題に対応できるツールは少ない。標準規格は、アナログの世界ではそれほど強力ではない。デジタルの世界でこそ力を発揮するものだ」とも述べている。

設計者にとって、SoCに求められる性能を満たすために、アナログ回路をデジタル制御するような回路の設計を行う機会が増えてくることが予想される。また、パッケージや電力供給の制限を超えないように、多くの機能を1チップに集積した上で、複雑な低消費電力モードを管理できるようにするためには、アナログ回路とデジタル回路の両方の機能を駆使した回路設計を行う必要があるだろう。これらの要求が、Accellera小委員会のAMSアサーション用言語を定義する取り組みを後押ししている。「研究者は、多くのSVAの考え方をアナログ回路にも拡張するため、残っている複数の論理的問題に取り組まなければならない。しかし、委員会は、部分的な仕様化と認定に注力するだろう」とLittle氏は言う。

同委員会は、技術者がデジタル回路ブロックの中でミックスドシグナル回路のアサーションを記述できるように、SVAをVerilog-AMSに加える方向で検討している。同委員会は、2011年内に発表するVerilog-AMSの最新バージョンに3つの新機能を組み込みたい考えだ。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング