SLVSインタフェースをFPGAで活用せよ:低消費電力の差動伝送規格(3/3 ページ)

VDSL2ラインカードへの応用

SLVSインタフェースは、データ通信や、ディスプレイにおける映像/画像データの高速かつ低消費電力での伝送など、さまざまな用途に利用されている。これらの用途では、ASICのSLVS入出力インタフェースから、SLVSコンパチブルなトランシーバが実装されているFPGAデバイスを介して、異なるデータプロトコルにブリッジする場合もある。

ここで、BroadcomのVDSL2(Very High Bit Rate Digital Subscriber Line 2)用ラインカードのリファレンス設計向けに、SLVSインタフェース機能とXAUI(10Gbps Attachment Unit Interface)の物理層をブリッジする機能を、Lattice SemiconductorのFPGAチップ「SC/M」で実現した事例を紹介しよう。

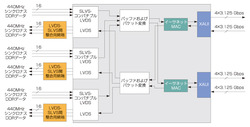

このVDSL2のリファレンス設計では、FPGAに6系統のSLVSチャネルが実装されている(図4)。このFPGAデバイスはSLVSのデータストリームとXAUIパケットの間をブリッジしている。BroadcomのDSL(Digital Subscriber Line)端末用ICは、FPGAの3系統のSLVSチャネルに対してデータを送信し、3系統のSLVSチャネルからデータを受信する。各チャネルは、18ビットのバス幅を備えており、FPGA内の標準SLVSポートとDSL端末用ICを接続している。

FPGA内部では、3系統のレシーバチャネルから任意に選択されたチャネルが、3系統のトランスミッタチャネルから任意に選択されたチャネルに接続される。これにより、所定のレシーバチャネルとトランスミッタチャネルが接続されるので、全てのDSL端末用ICの間が、FPGAを介して接続されていることになる。FPGAのもう一方の側では、伝送速度が3.125GbpsのSERDESインタフェースを8系統用いたイーサネットチャネルが2系統構築されている。

このFPGAの差動入出力ポートは、1チャネル当たり884Mbpsの伝送速度をサポートする。FPGAには、LVDSトランシーバおよびXAUIの物理層とともに、バッファリングとパケット変換のための機能ブロック2個と、イーサネットMAC(Media Access Control)ブロック2個が組み込まれる。これら4個の機能ブロックに使用されるLUT(Look Up Table)は1万5000個以下である。

Copyright © ITmedia, Inc. All Rights Reserved.