デジタル制御電源を学ぶ(4) 複雑な電源は機能分析から制御方式を見極める:Design Hands-on(3/3 ページ)

制御方式に従ってソフトウェアを記述する

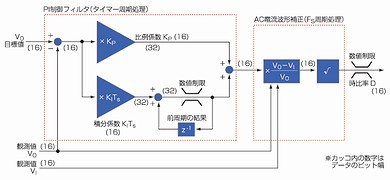

ソフトウェアの基本構成が準備できたら、電源の要求仕様に合った制御方式に従ってソフトウェアの記述を進めよう。これは、電圧制御の2つのCPU割り込み関数の記述に相当する。図4に、本稿のインターリーブPFC回路で電圧制御に適用したデジタル信号処理のブロック図を示す。

この図にある「PI制御フィルタ」については、前回のバックコンバータの解説を参照してほしい。図中の「AC電流波形補正」は、出力電圧の観測値と入力電圧の観測値の除算結果を求め、PI制御フィルタの演算結果に乗算して、平方根の近似演算を施したものだ。PI制御フィルタの演算結果が入力電流の実効値(または出力電流)に比例する。

このPI制御フィルタとAC電流波形補正を合わせたCPU所要サイクル数は、新日本無線の電源制御用DSC「NJU20011」では120サイクルで、CPUクロック周波数が60MHzのとき2.0μsに相当する。電圧制御に要するCPUの稼働時間は、スイッチング周期12.5μsの80%以下に納まることが確認できた。

最後にフィルタ係数を調整する

最後はフィルタ係数の調整である。PI制御フィルタの比例係数と積分係数(メモリ上に配置された数値データ)を調整する。この作業は、次の2つのステップに分けて進めていく。

まずは比例係数だ。積分係数をゼロに設定し、比例係数を大きくしながら出力電圧が発振する限界を確認する。そして今度は、全動作範囲(入力電圧や出力電流の全範囲)で所定の力率が得られるまで比例係数を小さくする。比例係数の調整は比例ゲインを調整する作業なので、通常、調整が終わった段階でもVO目標値からの誤差は大きい。この誤差を小さくするのが次のステップで、積分係数を調整する。これは積分ゲインの調整に相当し、比例係数の調整と同じ工程で調整する。

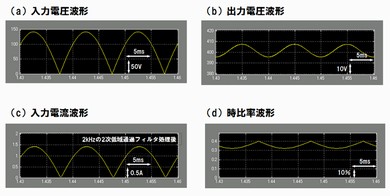

図5に、今回設計したインターリーブPFC回路の特性を数値演算ツールでシミュレーションした結果を示す。フィルタ係数を調整したデジタルフィルタを適用した。図5(b)中の出力電圧波形は所定の電圧範囲に収まり、図5(a)の入力電圧波形と図5(c)の入力電流波形は、AC電流波形補正により相似な波形になることが確認できた。

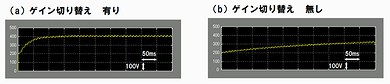

後は起動期間の確認だ。図6(b)は前記で調整したフィルタ係数のまま起動した場合の立ち上がり波形だ。出力電圧の変化に追従しないようにフィルタ係数を調整したのだから、これは当然の結果といえる。図6(a)は所定の出力電圧に到達するまでの期間、ゲインを高く設定した場合の立ち上がり波形だ。200ms以内に起動することが確認できた。環境の変化に合わせた制御の切り替えは、ソフトウェア処理であれば容易に行える。

さて、次回は最終回。本稿のAC-DCコンバータにさらに実用的な改良を加え、ソフトウェアによるデジタル制御のまとめとする。

エネルギーコントロール(Energy Control)特選コーナー

関連記事

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング