DSPと汎用組み込みマイクロプロセッサの比較:イチから学ぶDSP基礎の基礎(4)(1/2 ページ)

今回は、DSPと汎用の組み込み用マイクロプロセッサを比較します。

一口で組み込み用マイクロプロセッサといっても、外部バスを持たない小規模なコントローラ向けのものから工業用リアルタイムOSやLinuxが動く高機能のもの、PDAのCPUとして用いられているものまで、さまざまです。

一方、DSPもさほど演算能力を必要とされないモータ制御用のローエンドの製品から、複数の演算器と大容量のキャッシュまで搭載した最先端の製品まで、複数のバリエーションがあります。

あまり単純化して比較するのは無理がありますが、一般的なDSPのハードウェア面の特徴を挙げると、次のようになります。ただし現在市場に出回っているすべてのDSPが下記の特徴を有しているわけでもありませんし、組み込み用プロセッサでもこのような特徴を備えている場合があります(あくまでも一般的な特徴比較です[注])。

注:ここで用いている組み込み用マイクロプロセッサとは、パソコン用のプロセッサ以外の汎用のマイクロプロセッサを意味しています。また、文中で述べたDSPに関する記述の一部は、すべてのDSPに当てはまるわけではありません。DSPの一般的特徴として述べていることが、現在のTIのDSPには当てはまらない場合もありますので、ご注意ください。

(1)乗算器内蔵

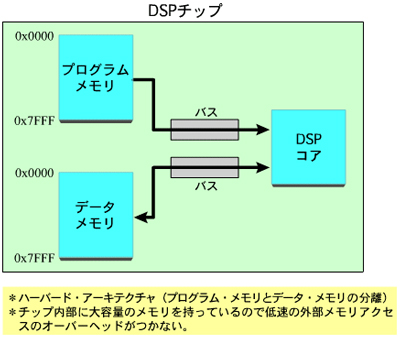

(2)ハーバードアーキテクチャ(データメモリとプログラムメモリの分離)

(3)演算能力に合わせたデータ転送能力を実現するための強力なI/O

(1)、(2)の特徴は、算術演算(乗算、加減算)主体の信号処理を高速で実行するためのものです。(3)は高速のA/D・D/Aコンバータなどを接続するためのもので、高速の同期シリアルポートや優れた機能を持つDMAコントローラを内蔵しているのが普通です。

これはデジタル信号処理に要求される、連続的に大量のデータを低遅延で算術演算(特に積和演算)するという目的を満たすための工夫です。

(1)、(3)とは逆に、組み込み用プロセッサの特徴を挙げるとすれば、文字列処理、テーブル処理用の命令セットや画像処理用のbitblt(bitblt=bit block transfer、ビットマップデータ転送)命令などがあります(ただし例外もあります)。

また、OSの実装を意識したMMU(Memory Management Unit:メモリ管理ユニット)は組み込み用プロセッサだけの特徴で、現在のところ、MMUを搭載したDSPはないようです。

組み込み用プロセッサも常に進化し続けているという点ではDSPと同じですが、DSPのようにデジタル信号処理に特化するのではなく、幅広いアプリケーションに対応できる総花的な処理能力向上とOS指向の機能強化を目指しています。

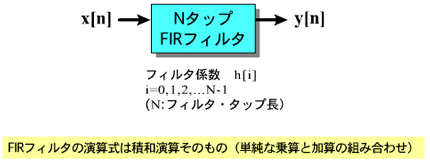

FIRフィルタ処理と積和演算

次にFIRフィルタを例に取って、DSPと組み込み用プロセッサを比較してみましょう。

y[n] = h[0]・x[n] + h[1]・x[n-1] + h[2]・x[n-2] + …… + h[N-1]・x[n-N+1](式1)

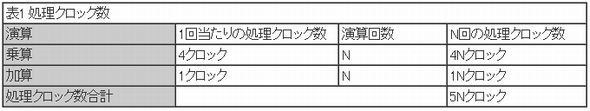

式1の積和演算は、乗算N回と加算N回の組み合わせです。1命令当たりの処理クロック数を乗算命令4クロック、加算命令1クロックとした場合のNタップFIRフィルタの演算に必要な処理クロック数は表1のようになります。

乗算器が16bit×16bit→32bit、加算の演算語長が32bitだった場合、FIRフィルタの連続的な積和演算中に加算処理でオーバーフローが生ずる可能性があります。オーバーフローを避けるために倍精度(64bit)で加算を行うと、FIRフィルタ処理に必要なクロック数はさらに増えます(速度が低下します)。

DSPでのFIRフィルタ処理

式1のFIRフィルタの計算手順は、下記に示すようにN回の積和演算の繰り返しになります。

ACC ← 0

ACC ← ACC+h[0]・x[n] 積和演算1回目

ACC ← ACC+h[1]・x[n−1] 積和演算2回目

ACC ← ACC+h[2]・x[n−2] 積和演算3回目

・・・・・・・・・・・・・・

ACC ← ACC+h[n−1]・x[n−N+2] 積和演算N回目

y[n] ← ACC

DSPは積和演算を1クロックで処理するから処理クロック数合計はNクロックです。クロック周波数が同一だとすると、演算に4クロック必要とする乗算器しか搭載していない組み込み用プロセッサによりも、DSPの方が5倍速くなります。

Copyright © ITmedia, Inc. All Rights Reserved.

画像1 DSPのメモリ構成の一例

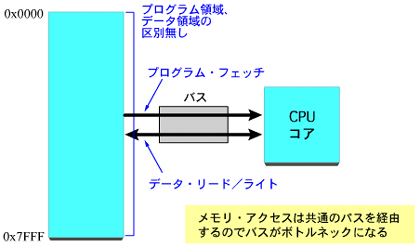

画像1 DSPのメモリ構成の一例 画像2 組み込み用プロセッサのメモリ構成の一例

画像2 組み込み用プロセッサのメモリ構成の一例

画像3 乗算器内蔵組み込み用プロセッサの一例

画像3 乗算器内蔵組み込み用プロセッサの一例