DSPと汎用組み込みマイクロプロセッサの比較:イチから学ぶDSP基礎の基礎(4)(2/2 ページ)

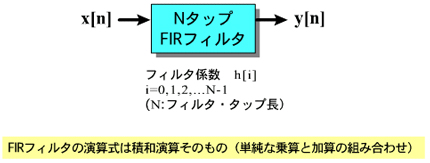

積和演算器の構成が16bit×16bit+40bit→40bitの場合、乗算16bit×16bit→32bitに対して、加算の演算語長(40bit)は8bit分の余裕があるので、FIRフィルタのタップ長Nが256(=28)以下ならオーバーフローは生じません。

連続的に積和演算を実行したときのオーバーフローを避けるために、DSPの積和演算器には必ず乗算器のビット幅(乗算結果の語長)よりも語長の大きい加算器が組み込まれています。

画像4 DSPの積和演算器の一例

画像4 DSPの積和演算器の一例クロック周波数:33MHz、乗算命令実行速度:1クロック(30ns)、積和演算命令:16bit×16bit+40bit→40bit、すべてのDSPは積和演算器を持ち、積和演算命令を備えてる。

以下、DSPと組み込み用プロセッサの比較を列挙していきます。

- クロック周波数が同じならば、チップ・トータルの消費電力は組み込み用プロセッサの方が低い

(DSP 500mW)>(組み込み用プロセッサ 330mW)

- クロック周波数が同じでも積和演算1回当たりの消費電力はDSPの方が低い

(DSP 15×10-6mW)<(組み込み用プロセッサ 50×10-6mW)

- 積和演算をするならばDSPは5分の1のクロック周波数で組み込み用プロセッサと同一の処理が可能(DSPはクロック周波数33MHz/5=6.6MHzで、クロック周波数33MHzの組み込み用プロセッサと同じ積和演算能力を持つ)。また、CMOS LSIの消費電力はクロック周波数に比例するので、DSPのクロックを5分の1に落とした場合のチップ・トータルの消費電力を比較すると、DSPの方が消費電力が低い

(DSP 500/5=100mW)<(組み込み用プロセッサ 330mW)

このように、カタログ上でのスペックは、組み込み用プロセッサの方が低消費電力に見えても、デジタル信号処理のアプリケーションでは積和演算速度の差からクロック周波数を落として使えるDSPの方が、低消費電力になります。

DSPと組み込み用プロセッサの差異は薄れつつあるように見える

最近はこれまでに挙げたようなDSPと組み込み用プロセッサのハードウェア的な差異は薄れつつあります。それは製造技術の進歩によりLSIの集積度が飛躍的に向上し、それぞれがお互いのハードウェアの特徴を取り込む形で進歩を遂げてきたからです。

集積度は飛躍的と比較するとクロック周波数の向上が頭打ち傾向にある中で、DSPも組み込み用プロセッサも同じような回路設計手法を用いて演算能力強化を図ろうとしているのですから、だんだん互いにハードウェアの特徴が似通ってくるのは当然といえば当然です。

例えばDSPでも画像処理向けの機能を備えたものがあり、組み込み用プロセッサでも乗算器を内蔵したものが出てきています。

しかしながら、これからもDSPはDSP、組み込み用プロセッサは組み込み用プロセッサとしてすみ分けていくでしょう。なぜならば両者にはハードウェア以外の差異も大きいからです。

Copyright © ITmedia, Inc. All Rights Reserved.