商用電源(100V)を直接マイコンの端子に接続できますか?:Q&Aで学ぶマイコン講座(9)(2/3 ページ)

GPIO端子の内部構造

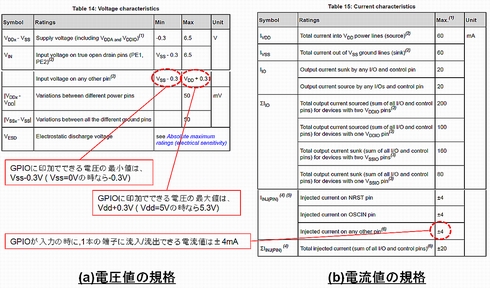

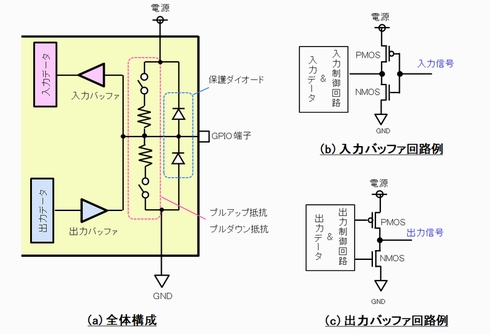

一般的なGPIOの構成図を図3に示します。GPIOは、入力データを受け取る入力バッファ、出力データを出力する出力バッファ、GPIOの電位を強制的に固定するプルアップ/プルダウン抵抗、そして外部からのサージ電圧を電源/GNDに逃がす保護ダイオードで構成されています。GPIOを入力として使用する場合は、出力バッファとプルアップ/プルダウン抵抗がOFFなのでGPIOはハイインピーダンス(H−Z)状態です。この時に、電源電圧よりも高い電圧、またはGNDよりも低い電圧が印加されると、保護ダイオードが順方向になり、電流が流れてGPIOを保護します。しかし、保護ダイオードにも流せる電流の限界があるので、それ以上大きな電流が流れると破壊します。図2(b)で示されたinjected currentがこの値になります。この表からSTM8Sの場合、最大±4mAしか流してはいけないことが分かります。GPIO端子に接続する電流制限抵抗は、この値を元に算出します。

また、GPIO端子に印加する電圧が大きい場合も破壊を引き起こします。図2(a)で示された電圧以上を印加しないように分圧抵抗を算出します。

具体的にSTM8S005を使って回路設計してみましょう。

電流制限抵抗と分圧抵抗の計算

最初に電流制限抵抗を計算しましょう。この時、分圧抵抗はないものとし、GPIO端子に電流が流入/流出しても、マイコンが破壊しないような電流値に設定します。

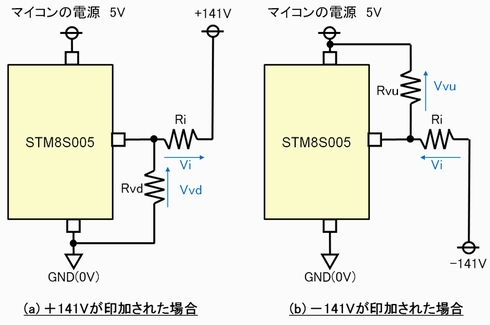

図2(b)に示されたように、±4mA以上流れないように抵抗値を算出します。端子に正電圧が印加された場合、Vdd側に付いている保護ダイオードが順方向になりますので、電流制限抵抗の両端には、+141VとVdd(ここでは5V)の電位差、すなわち141V−5V=139Vが印加されます。オームの法則から、139V/4mA=34.75kΩ以上にすれば、4mA以下の電流になることが分かります。負電圧の場合はどうでしょう。負電圧が印加されるとGND(Vss)側に付いた保護ダイオードが順方向になり、この時の電位差は141Vになります。141V/4mA=35.25kΩ以上にすれば、4mA以下の電流になることが分かります(厳密には保護ダイオードの順方向電圧を考慮して計算しなくてはなりませんが、141Vに比べたら非常に小さいので、ここでは無視します)。

スペック上はこの値で良いのですが、短絡事故などがあった場合を考えて、1桁くらい余裕を見たほうが良いでしょう。また、この抵抗値をそのまま使うと常時4mAも流れることになります。システムの消費電流を考慮すると、なるべく消費電流を抑えるべきですので、もう少し抑えてマイクロアンペアレベルにした方が賢明です。さらに抵抗値は大きいほど、微調整しやすいので、今回は1MΩ程度の抵抗を使うことにします。

そこで、電流制限抵抗を約1MΩにすると仮定して、次に分圧抵抗を計算してみましょう。

まず+141Vが印加された場合を考えます。

図4(a)の場合、GPIO端子とGNDにつながれた抵抗Rvdと電流制限抵抗Riで+141Vを分圧して5VがGPIO端子に印加されるようする必要があります。Rvd:(Rvd+Ri)=5V:141Vの関係が成り立てば良いことになります。すなわちRvd:Ri=5:136=1:27.2の関係になります。実験室で約1MΩの抵抗値で、この関係を満たす抵抗器を探してみると、ちょうど33kΩと930kΩを見つけたので、Rvd=33kΩ、Ri=930kΩにします。この場合Rvd:Ri=33:930=1:28.1になります。

次に−141Vが印加された場合(図4(b))にGPIO端子に約0Vが印加されるような分圧抵抗を計算する必要があります。一方で、AC0Vの点も考慮する必要があります。すなわち、印加電圧が+141Vから−141Vに変化する途中に0Vを通過します。この時がAC電圧のちょうど半分になるので、GPIO端子に印加される電圧も、ちょうど半分にする必要があります。そこで−141Vを印加する場合の分圧抵抗Rvuも先ほどのRvdと同じ33kΩにしなくてはなりません。するとRvu=33kΩとRi=930kΩで5V+141V=146Vの電位差を分圧することになります。Vi=146V×(33kΩ/(963+33)kΩ)=141Vとなって、GPIO端子の電圧は−141+141V=0Vになります。

これらの結果として図1の回路が得られます。

Copyright © ITmedia, Inc. All Rights Reserved.