400万ロジックセルを集積、20nm FPGAの出荷を開始:ザイリンクス Virtex UltraScale VU440

ザイリンクスは、20nmプロセス技術を用い400万ロジックセルを集積した最新のFPGA「Virtex UltraScale VU440」の出荷を始めた。次世代ASICあるいはSoCのプロトタイピングなどの用途に向ける。

ザイリンクスは2015年1月、20nmプロセス技術を用い400万ロジックセルを集積した最新のFPGA「Virtex UltraScale VU440」の出荷を始めたと発表した。次世代ASICあるいはSoCのプロトタイピングなどの用途に向ける。

VU440は、5000万以上のASICゲートに相当し、競合製品に比べて4倍の集積度を実現している。ユーザーI/O数は1456端子を備えている。バックプレーン動作に対応可能な48個の16.3Gビット/秒トランシーバや、89MビットのブロックRAMなども内蔵した。この集積度は、現行のVirtex-7 2000Tに比べて2倍以上の規模になるという。また、ASICと同様なクロックアーキテクチャの導入や、最新の配線技術および利用効率の高いロジックブロックの採用、といった特長を備えている。

VU440は、TSMCの第2世代SSI(スタックド シリコン インターコネクト)技術を用いて量産する。CoWoS(Chip-on-Wafer-on Substrate)3D ICプロセスで構築したSSI技術は、28nmプロセスですでに量産の実績がある。20nmプロセス技術を用いる第2世代SSI技術は、より大規模な回路を、小さいチップサイズに集積することができる。また、28nm製品に比べて、ダイ間を接続する帯域幅を5倍に広げたほか、スライス境界を超えたクロッキングアーキテクチャに対応したことから、高性能で低消費電力のSoCを実現することができるという。

関連記事

ザイリンクスが28nmFPGA「Artix-7」に車載対応品を追加、「Zynq」を補完

ザイリンクスが28nmFPGA「Artix-7」に車載対応品を追加、「Zynq」を補完

ザイリンクスは、車載ICの品質規格であるAEC-Q100に準拠するFPGA製品群「XA FPGA」に、「Xilinx 7シリーズ」の中でもコストと消費電力を低く抑えたことを特徴とする「Artix-7」を追加した。 ザイリンクス、20nmプロセス採用FPGAのサンプル出荷を開始

ザイリンクス、20nmプロセス採用FPGAのサンプル出荷を開始

ザイリンクスは11月11日(米国時間)、台湾のTSMCの20nmプロセスを採用したFPGA製品の初期サンプルを出荷したと発表した。一般顧客向けサンプルの出荷は2014年1〜3月から開始する。 FPGA「Artix-7」の設計生産性を高める評価キットが利用可能に

FPGA「Artix-7」の設計生産性を高める評価キットが利用可能に

AC701はFPGA「Artix-7」用の評価キットである。同評価キットを活用することで、Artix-7を使ったシステムの開発と検証を効率よく行うことができる。 ザイリンクスが400Gb イーサネットの動作デモを公開――20nmFPGAで

ザイリンクスが400Gb イーサネットの動作デモを公開――20nmFPGAで

Xilinx(ザイリンクス)は2014年11月、エンジニアリングサンプル(ES)出荷段階にある20nmプロセスを用いたFPGA「Virtex UltraScaleファミリ XCVU095」を使用した400Gビット イーサネットの動作デモを公開した。 ザイリンクス、20nmプロセスFPGAをテープアウト――製品戦略反映し呼称も「8」ではなく「UltraScale」

ザイリンクス、20nmプロセスFPGAをテープアウト――製品戦略反映し呼称も「8」ではなく「UltraScale」

ザイリンクスは、20nmプロセス技術を用いたFPGAのテープアウト(設計完了)を発表した。同時に、20nmプロセス採用FPGAなどに適用する新世代アーキテクチャ「UltraScale」の概要も公表した。新プロセス、新アーキテクチャを採用した製品の出荷は2013年10〜12月を予定している。

Copyright © ITmedia, Inc. All Rights Reserved.

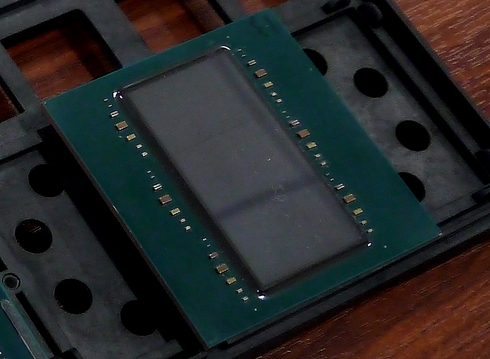

「Virtex UltraScale VU440」のダイ写真

「Virtex UltraScale VU440」のダイ写真