制御回路の確認から効率改善、仕様適合チェックまで:覚えておきたい「電源測定」のきほん手順(2)

今回は、プロトタイプの電源測定の続きです。デジタル/アナログ制御回路のデバッグからリップル、ノイズ、短絡の回路保護、トランジェント応答、効率などの仕様に適合しているどうかのチェックまでを行います。

前回(第1章)では、部品/デバイスの選択と、最初のプロトタイプの低電圧/高電圧回路のテストを含む測定手順について説明しました。第2章では、まずデジタル/アナログ制御回路のデバッグから始めます。

設計で最も難しい制御ロジックをチェック

ここでは、最も重要で、言うまでもなく設計で最も難しいところである制御ロジックをチェックします。補正、電圧、タイミング、周波数応答をテストする必要があります。まず、スイッチング周波数、パルス幅とデューティサイクル、さまざまな負荷を検証します。これを実行するには、電源投入時のスイッチングデバイスにおける変調信号を測定します。次に、制御ループのワイドバンド インジェクション トランスフォーマから周波数スイープ信号を入れ、ループ周波数をチェックします。最後に、周波数応答アナライザで回路のゲインと位相を測定します。

スイッチング特性を確認

高電圧回路、低電圧回路、制御ロジック信号の検証ができたならば、パワー段のスイッチング特性をチェックします。無負荷時、通常の負荷時、全負荷時におけるスイッチング特性をテストします。全てのスイッチ(MOSFET、IGBTなど)のターンオン、ターンオフ、デューティサイクル、デッドタイムが期待通りになっていることをダブルチェックします。全てのVGS信号にノイズ、バンプがないことを確認し、この端子の意図されないグリッチによって意図しないターンオンやシュートスルーがないことを確認します。

トポロジによっては、同期する整流器またはHブリッジのデッドタイムをチェックする必要があります。これにより、シュートスルーの可能性がないことを確認できます。全てが期待通りであることを確認するためには、ゲートドライバと他の関連する信号間のタイミング関係を検証します。

効率を正しく把握する

通常、効率が設計の第1目標ですので、設計プロセスで発生するどのような損失であっても最小にすることが重要です。特に、最新の高効率設計では、パワースイッチと磁気回路のスイッチング損失と導通損失はシステムの損失全体において大きな割合を占めます。

データシートの仕様から単純にスイッチング/導通損失を計算することは、間違いの原因になるだけでなく、大きく異なった結果になることがあるためお勧めできません。これは、動作条件や回路寄生のもとになる総合的な損失プロファイルが分からないためです。回路が有効になり、負荷がかかった場合の整流器、スイッチ(MOSFET、IGBTなど)、磁気回路の損失もチェックします。大抵の場合、磁気回路はカスタム設計であり、スイッチングデバイス同様、動作時でのテストが重要になります。このようにすることで、磁気回路を正しく評価できます。

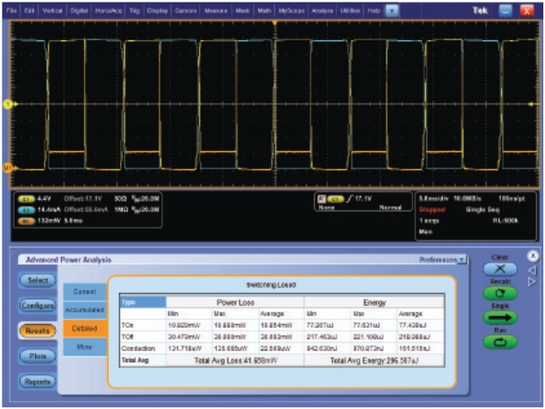

オシロスコープでスイッチング損失を測定する場合、電圧と電流を掛け算し、ターンオン、ターンオフにおける電力波形の平均値をとります。図1に示すパワー解析ソフトウェアを使用すると、簡単に、優れた再現性で実行できます。

仕様の確認

次は、設計が商用電源や負荷の規制、リップル、ノイズ、短絡の回路保護、トランジェント応答、効率などの仕様に適合していることを確認します。

負荷規制では、電源の入出力端子で高確度のデジタルマルチメータ(DMM)を使用し、入力電圧を一定に保ちながら負荷を最小から最大まで連続的に変化させます。これは、再現性のある結果を得るために重要です。出力電圧対負荷の変化のログをとり、負荷変動を確認します。

負荷変動も同様の手順でテストできます。一定負荷における出力電圧を測定しながら、AC入力電圧を最小値から最大値まで連続的に変化させます。このテストは、ユニバーサル入力電源では特に重要です。高分解能測定に最適化されたオシロスコープまたは高確度グラフィカル サンプリングDMMを使用して、全負荷時におけるリップルとノイズをチェックします。一般的に、オシロスコープは広帯域ですが、DMMの方が高確度です。パワーアナライザを使用すると、全ての動作条件で入力電圧と出力負荷を変化させて効率のログをとることができます。

前回から今回までの測定手順が終われば、電源設計のゴールは間近です。次回、第3章では、コンプライアンスと検証テストを考察します。

関連記事

部品選定から低電圧/高電圧回路測定まで

部品選定から低電圧/高電圧回路測定まで

電源設計に求められる要件は、多くなっています。高効率/高電力密度、迅速な市場投入、規格への対応、コストダウンなどを考慮せざるを得ず、電源設計におけるテスト要件も複雑化しています。そこで、本連載では、3回にわたって、複雑な電源設計プロセスの概要と、プロセスごとのテスト要件について説明していきます。 シーケンサの修理(1)4級アンモニウム塩との闘い

シーケンサの修理(1)4級アンモニウム塩との闘い

シーケンサの修理依頼があった。例のごとく、電源が壊れているようで、修理を進めていくと、コンデンサの液漏れが確認された。洗浄し、部品を取り換え、修理完了と思いきや……。今回から数回にわたり、このシーケンサ修理の様子を紹介する。 電源制御ループの周波数特性を測る

電源制御ループの周波数特性を測る

本稿では、スイッチング電源回路のフィードバック制御ループの利得と位相の周波数特性を測定する手法を紹介する。測定にはネットワークアナライザは使わず、信号発生器とオシロスコープ、トランスを利用して、自らボード線図を描くことで特性を把握する。本稿の内容を、周波数特性評価の基本手法として活用していただければ幸いである。 電源制御ICでミリオーム・メーターを作る

電源制御ICでミリオーム・メーターを作る

古いレギュレーターICを使って、ミリオーム・メーターを簡単に作る方法を紹介する。

Copyright © ITmedia, Inc. All Rights Reserved.

パワー解析ソフトウェアにより、スイッチング損失、導通損失を自動的に測定できる。写真は、テクトロニクスMSO5000Bシリーズ・オシロスコープ上で実行する「DPOPWR」のキャプチャ

パワー解析ソフトウェアにより、スイッチング損失、導通損失を自動的に測定できる。写真は、テクトロニクスMSO5000Bシリーズ・オシロスコープ上で実行する「DPOPWR」のキャプチャ